Dispositivos Lógicos Programables

Anuncio

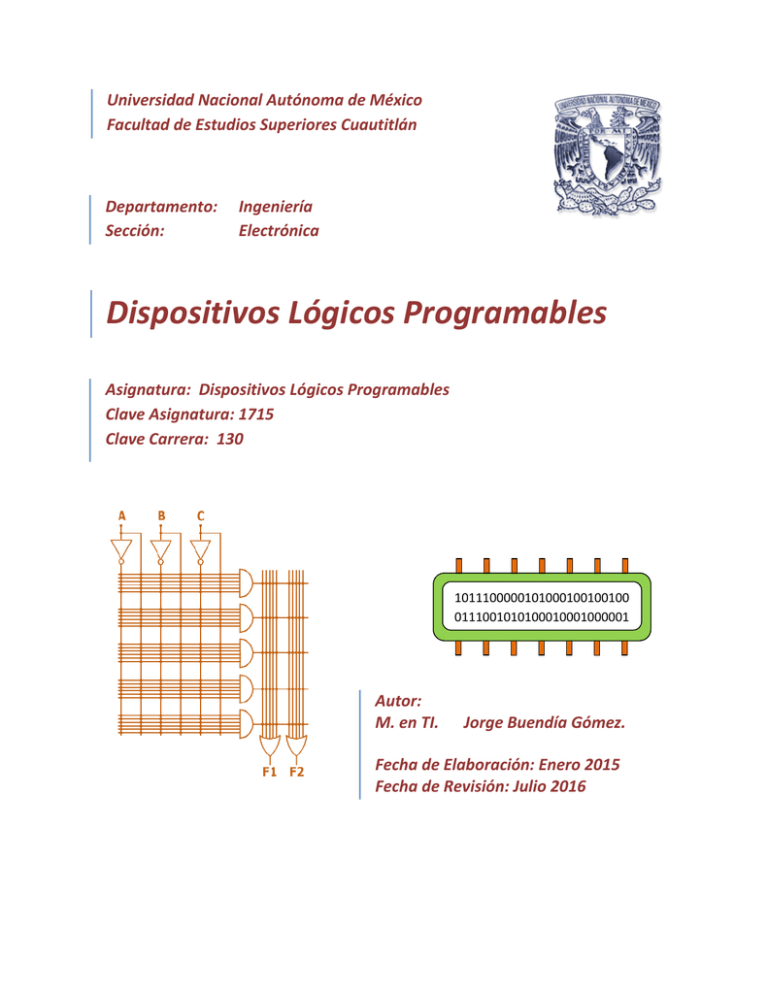

Universidad Nacional Autónoma de México Facultad de Estudios Superiores Cuautitlán Departamento: Sección: Ingeniería Electrónica Dispositivos Lógicos Programables Asignatura: Dispositivos Lógicos Programables Clave Asignatura: 1715 Clave Carrera: 130 1011100000101000100100100 0111001010100010001000001 Autor: M. en TI. Jorge Buendía Gómez. Fecha de Elaboración: Enero 2015 Fecha de Revisión: Julio 2016 Facultad de Estudios Superiores Cuautitlán UNAM Laboratorio de Dispositivos Lógicos Programables Índice Índice I Prólogo II Reglamento V Práctica 1 Memorias EEPROM 1 2.3 Memorias de solo lectura (ROM’s) Práctica 2 Comparador de Magnitud 5 2.3 Memorias de solo lectura (ROM’s) Práctica 3 Contador Digital de la Sucesión de Fibonacci 8 2.3 Memorias de solo lectura (ROM’s). Práctica 4 Display Alfanumérico 7x5 con 2 máquinas secuenciales 12 2.3. Memorias de solo lectura (ROM’s). Práctica 5 Decodificador de Teclado con GAL y algebra de Boole 16 2.6. Arreglos lógicos genéricos (GAL’s). Práctica 6 Implementación de Tablas de Verdad con GALs 22 2.6. Arreglos lógicos genéricos (GAL’s). Práctica 7 Control de Potencia con Flip Flops en dispositivos PLD 28 2.6. Arreglos lógicos genéricos (GAL’s). Índice I Facultad de Estudios Superiores Cuautitlán UNAM Laboratorio de Dispositivos Lógicos Programables Prólogo Objetivo del curso Al finalizar el curso el alumno conocerá y comprenderá la estructura y funcionamiento de los dispositivos lógicos programables (PLD) empleados en el diseño de sistemas digitales de última generación, así mismo podrá diseñar e implementar dispositivos con circuitos programables de muy alta escala de integración. Objetivos del Laboratorio Analizar y comprobar los fundamentos de los dispositivos lógicos programables (PLD’s). Implementar circuitos electrónicos que empleen PLD’s para realizar el control del sistema. Conocer las diferentes arquitecturas empleadas en la construcción de PLD’s y aplicarlas de acuerdo al diseño del sistema. Conocer y utilizar las herramientas de hardware y software necesarias para la implementación de los circuitos que contienen PLD’s. Introducción Un PLD (Programmable Logic Device, Dispositivo Lógico Programable) es un dispositivo electrónico empleado para la implementación de diseños digitales. A diferencia de las compuertas lógicas, un PLD es un arreglo genérico que no realiza una función definida. Para que el dispositivo pueda ser utilizado, este debe ser programado para indicarle las conexiones que deberán realizarse internamente. Un PLD está formado por una matriz de compuertas AND y puertas OR, que se pueden programar para conseguir funciones lógicas específicas. Existen varios tipos de dispositivos que se clasifican como PLD. PROM (Programmable Read Only Memory). Memoria programable de sólo lectura. PLA (Programmable Logic Array). Arreglos Lógicos Programables. PAL (Programmable Array Logic). Lógica de Arreglos Programables. GAL (Generic Array Logic). Arreglos lógicos genéricos. CPLD (Complex Programmable Logic Device) Dispositivos Lógicos Programables Complejos. FPGA (Field Programmable Gates Array ) Arreglos de Compuertas Programables de Campo. Todos los PLD están formados por matrices de NOT, AND y OR programables. Básicamente, una matriz programable es una red de conductores distribuidos en filas y columnas con un fusible en cada punto de intersección. Las matrices pueden ser fijas o programables. Los PLD’s presentan muchas ventajas sobre los circuitos discretos implementados con compuertas básicas de baja escala de integración (SSI) y de mediana escala de integración (MSI), estas características se pueden identificar como: Prólogo II Facultad de Estudios Superiores Cuautitlán UNAM Facilidad de diseño. Prestaciones. Fiabilidad. Economía. Seguridad. Además de los puntos mencionados, podemos añadir que los PLDs facilitan el ruteado de las placas de circuito impreso debido a la libertad de asignación de terminales de este tipo de dispositivos. En este laboratorio se realizarán circuitos PLD’s que abarcan la utilización de las diferentes herramientas de diseño de software y hardware para implementar diferentes diseños. Es importante recalcar que el alumno deberá comprender la necesidad de interacción entre las diferentes áreas de la Ingeniería para llevar a la práctica un sistema digital que emplee este tipo de dispositivos programables. Entre estas áreas se distinguen: Electrónica Control Analógico Control Digital Diseño Lógico Computación Diseño de Software Electrónica de Potencia Mecánica Motores y algunas áreas adicionales. Instrucciones para la elaboración del reporte Será necesario incluir en cada actividad previa y reporte de práctica, una portada (obligatoria) como la mostrada a continuación. U. N. A. M. F. E. S. C. Laboratorio de : ________________________________________ Grupo: ________________________________________ Profesor: ________________________________________ Alumno: ________________________________________ Nombre de Práctica: ________________________________________ No. de Práctica: ________________________________________ Fecha de realización: ________________________________________ Fecha de entrega: ________________________________________ Semestre: ________________________________________ Para la presentación del reporte se deberá cumplir con los requisitos indicados en cada una de las prácticas, incluyendo: Prólogo III Facultad de Estudios Superiores Cuautitlán UNAM Actividades previas Introducción Procedimiento experimental Circuito armado Tablas de datos Mediciones Gráficas Comentarios Observaciones Esquemas Diagramas Cuestionario Conclusiones y en general todos los elementos solicitados dentro del desarrollo de la práctica. Los criterios de evaluación para el laboratorio son los siguientes: C1 (Criterio de evaluación 1): Actividades previas (40%) C2 (Criterio de evaluación 2): Habilidad en el armado de circuitos (10%) C3 (Criterio de evaluación 3): Desarrollo y funcionalidad de la práctica (10%) C4 (Criterio de evaluación 4): Reporte entregado con todos los puntos indicados (40%) Bibliografía 1. Pardo Fernando, Boluda José A., VHDL Lenguaje para síntesis y modelado de circuitos, México,1ª Edición, Alfa Omega RA-MA, 2000. 2. García Iglesias Jose M, Dispositivos Lógicos Programables (PLD) Diseño práctico de aplicaciones, México, RA- MA, 2006. 3. Bolton W. Programmable Logic Controllers ,5th, Elservier-Newnes, USA 2009. 4. Parr E.A., Programmable Controllers, 3th, An Engineer´s Guide- Newnes, USA 2003. 5. Grediaga Olivo Angel, Diseño de Procesadores con VHDL, España, Universidad de Alicante, Servicio de Publicaciones, 2007. 6. Machado Sánchez Felipe, Diseño Digital Avanzado con VHDL, México, Dykinson S.L. Libros, 2009. 7. Urquía Moraleda, Diseño de Hardware Digital con VHDL, Colombia, UniversidadNacional de Educación a Distancia, 2008. 8. Mandado Enrique, Dispositivos Lógicos Programables y sus Aplicaciones, España, Thomson Paraninfo, 2002. 9. Serna Ruiz Antonio, Lógica Digital y Microprogramable, España, Thomson Paraninfo, 2000. Prólogo IV Facultad de Estudios Superiores Cuautitlán UNAM Laboratorio de Dispositivos Lógicos Programables Reglamento Interno de los Laboratorios de Comunicaciones, Control, Sistemas Analógicos y Sistemas Digitales 1. Dentro del laboratorio queda estrictamente prohibido. a. b. c. d. e. Correr, jugar, gritar o hacer cualquier otra clase de desorden. Dejar basura en las mesas de trabajo y/o pisos. Sentarse sobre las mesas Fumar, Introducir alimentos y/o bebidas. Utilizar cualquier objeto ajeno a las prácticas de laboratorio, tales como: celulares o equipos de sonido (aun con audífonos) excepto algún equipo para realizar las prácticas f. La presencia de personas ajenas en los horarios de laboratorio. g. Dejar los bancos en desorden. h. Mover equipos o quitar accesorios de una mesa de trabajo a otra sin el consentimiento previo del profesor de laboratorio en turno. i. Usar o manipular el equipo sin el conocimiento previo del profesor. j. Rayar las mesas del laboratorio. k. Energizar algún circuito sin antes verificar que las conexiones sean las correctas (polaridad de las fuentes de voltaje, multímetros, etc.). l. Hacer cambios en las conexiones o desconectar equipo estando éste energizado. m. Hacer trabajos pesados (taladrar, martillar, etc.) en las mesas de las prácticas. 2. El alumno verificará las características de los dispositivos electrónicos con el manual. 3. Es responsabilidad del alumno revisar las condiciones del equipo del laboratorio al inicio de cada práctica y reportar cualquier anomalía que pudiera existir (prendido, dañado, sin funcionar, maltratado, etc.) al profesor del laboratorio correspondiente. 4. Es requisito indispensable para la realización de las prácticas, que el alumno cuente con su manual completo y actualizado al semestre en curso, los cuales podrán obtener en: http://olimpia.cuautitlan2.unam.mx/pagina_ingenieria. 5. El alumno deberá traer su circuito armado para poder realizar la práctica, de no ser así no podrá realizar dicha práctica (donde aplique) y tendrá una evaluación de cero. 6. Para desarrollar trabajos, o proyectos en las instalaciones de los laboratorios, es requisito indispensable que esté presente el profesor responsable, en caso contrario no podrán hacer uso de las instalaciones. 7. Correo electrónico del buzón para quejas y sugerencias para cualquier asunto relacionado con los Laboratorios ([email protected]) 8. La evaluación del laboratorio, será en base a lo siguiente: A - (Aprobado); Cuando el promedio total de todas las prácticas de laboratorio sea mayor o igual a 6 siempre y cuando tengan el 90% de asistencia y el 80% de prácticas acreditadas en base a los criterios de evaluación. Reglamento Interno de los Laboratorios de Comunicaciones, Control, Sistemas Analógicos y Sistemas Digitales V Facultad de Estudios Superiores Cuautitlán UNAM NA - (No Aprobado); No se cumplió con los requisitos mínimos establecidos en el punto anterior. NP - (No Presentó); con o sin asistencia pero que no haya entregado reporte alguno. 9. Los casos no previstos en el presente reglamento serán resueltos por el Jefe de Sección. NOTA: En caso de incurrir en faltas a las disposiciones anteriores, el alumno será acreedor a las siguientes sanciones por parte del profesor de laboratorio según sea el caso y la gravedad, baja temporal o baja definitiva del grupo de laboratorio al que está inscrito Reglamento Interno de los Laboratorios de Comunicaciones, Control, Sistemas Analógicos y Sistemas Digitales VI Práctica 1 Memorias EEPROM 1. 2. Laboratorio de Dispositivos Lógicos Programables Práctica 1 Memorias EEPROM Tema: 2.3 Memorias de solo lectura (ROM’s) Objetivos Implementar un circuito multiplicador de 2 números de 4 bits cada uno. Programar la memoria EEPROM con la tabla de verdad del multiplicador. Comprobar el funcionamiento del multiplicador. Introducción En esta práctica realizaremos el diseño de un circuito que multiplique 2 números de 4 bits cada uno, por lo que se requiere un total de 8 entradas y por lo tanto 256 combinaciones (2 8). El multiplicando A está formado por las variables (A3A2A1A0) y el multiplicador B está formado por los bits (B3B2B1B0). Dado que cada factor es de 4 bits, el producto máximo de salida es 15 x 15 = 225 y por lo tanto el producto deberá expresarse en 8 bits (P7P6P5P4P3P2P1P0). Unos de los circuitos programables básicos son las memorias de solo lectura ya que pueden almacenar en ellas de forma directa las tablas de verdad que representan a los sistemas digitales, estas memorias tienen una capacidad de almacenamiento definida por el tamaño de sus bus de direcciones (n líneas) y el tamaño de su bus de datos (m líneas) y por lo tanto pueden resolver sistemas que tengan n entradas por m salidas. Una gran ventaja de la utilización de estas memorias es que no se requiere la reducción algebraica de los términos a través de algebra de Boole o Mapas de Karnaugh ya que la tabla deberá ser insertada en su totalidad y cada dirección accesada proporcionará una de las combinaciones de la tabla. En esta práctica utilizaremos una memoria AT28C16 cuya capacidad es de 2K x 8 y por lo tanto es capaz de almacenar tablas de 11 entradas (2048 combinaciones de entrada) y puede proporcionar hasta 8 salidas independientes. Fig. 1.1 Terminales de la memoria AT28C16 Dispositivos Lógicos Programables 1 Práctica 1 Memorias EEPROM Actividades previas a la realización de la práctica 1. 2. 3. 4. 5. El alumno deberá realizar la lectura de la práctica. El alumno definirá los valores que representan a la multiplicación de los 2 números de 4 bits. El alumno generará el archivo binario MULT4x4.BIN empleando el software del programador SuperPro, para ello deberá insertar la tabla de 256 valores que representan a los productos posibles de la operación de multiplicación. El alumno realizará la simulación del circuito del procedimiento experimental considerando la figura 1.5 siguiendo los pasos del desarrollo. Considere emplear el circuito de memoria 2732 en sustitución del circuito AT28C16 de la práctica, considerando que tiene una terminal de direcciones extra y no tiene la terminal WE. Esta sustitución es necesaria debido a que el simulador no tiene un modelo de simulación para la memoria AT28C16. Entregar los resultados de la simulación de forma impresa al profesor al inicio de la sesión de laboratorio. Material 1 Memoria AT28C16 8 Resistencias de 330 Ω 1 Barra de 8 leds ó en su defecto 8 leds individuales. Equipo 1 Fuente de voltaje de CD. 1 Multímetro 1 Programador Universal 1 Protoboard Procedimiento Experimental 1. Generar la tabla de valores en el editor de buffer del software SuperPro como se muestra en la figura 1.2. Considere que solo están mostrados los productos desde 0 x 0 = 0 hasta 4 x 3 = 0C y deberá llenarse hasta F x F = E1 4 x 3 = 0C F x F = E1 Fig. 1.2 Ejemplo de Tabla de valores del multiplicador 2. Salvar el buffer en formato binario seleccionando la pestaña de Archivo/Guardar y asignando el nombre MULT4x4, designe la carpeta de almacenamiento que desee como se muestra en las figuras 1.3 y 1.4. Dispositivos Lógicos Programables 2 Práctica 1 Memorias EEPROM Fig. 1.3 y 1.4 Pestaña de selección de Archivo y Nombre de archivo 3. 4. Programe la memoria AT28C16 con archivo MULT4x4.BIN Implemente el circuito de la figura 1.5. Figura 1.5 Multiplicador de 4 x 4 bits 5. 6. Compruebe la función de multiplicación del circuito proponiendo una tabla de 8 valores para el multiplicando y 8 valores para el multiplicador. Llene la tabla 1.1 con los valores obtenidos del circuito y verifique que la operación se está realizando correctamente. Multiplicando Multiplicador Producto Tabla 1.1 7. 8. El alumno diseñará un sistema que obtenga el código gray, el código XS3, el código en complemento a 2 y el código BCD8421 a partir de un código binario de 4 bits. Considere que para los 3 primeros códigos la salida es en 4 bits y que para el código BCD8421 se requieren 8 bits para la representación de los números 10, 11, 12, 13, 14 y 15. Dispositivos Lógicos Programables 3 Práctica 1 Memorias EEPROM 9. 10. 11. 12. Se deben incluír señales de control que seleccionen cuál es el código que se desea mostrar a la salida. El alumno determinará las conexiones de la memoria EEPROM AT28C16. El alumno implementará el circuito y lo probará en el laboratorio. El alumno comprobará las 4 tablas de verdad. Cuestionario 1. 2. Diseñe un multiplicador de 4 bits x 4 bits en forma discreta y dibuje el circuito resultante con compuertas lógicas de cualquier número de entradas. Compare el circuito resultante con respecto al circuito implementado en esta práctica. Explique las ventajas y desventajas de los circuitos implementados con memoria ROM. Dispositivos Lógicos Programables 4 Práctica 2 Comparador de Magnitud Laboratorio de Dispositivos Lógicos Programables 1. 2. Práctica 2 Comparador de Magnitud Tema: 2.3. Memorias de solo lectura (ROM’s). Objetivos Implementar un circuito comparador de magnitud de 2 números de 4 bits cada uno. Programar la memoria EEPROM con la tabla de verdad del comparador. Comprobar el funcionamiento del comparador Introducción El comparador es un circuito que nos permite determinar la relación de magnitud entre dos datos (A y B), posibilitando definir: 1 bit de salida para indicar si el dato A > dato B 1 bit de salida para indicar si el dato A < dato B 1 bit de salida para indicar si el dato A = dato B dato A A>B CComparador de Magnitud de 4 bits A<B A= B dato B Fig. 2.1 Comparador de magnitud de 4 bits Debido a que para este circuito se requieren 4 entradas para cada uno de los datos entonces se ocuparán 8 direcciones de una memoria y 256 de sus localidades y se tendrán 3 salidas que determinarán cada uno de los estados del comparador, la salida se activará si se cumple la condición. La implementación de este circuito en forma discreta con compuertas lógicas tiene la dificultad de que los minitérminos resultantes de la reducción, son términos con muchas variables y algunos de ellos no se pueden reducir debido a que forman una diagonal en un mapa de Karnaugh. La salida A = B tiene por lo tanto 16 minitérminos de 8 variables cada uno produciendo consecuentemente un circuito de gran escala. Actividades previas a la realización de la práctica 1. 2. El alumno deberá realizar la lectura de la práctica. El alumno definirá la tabla de verdad del sistema de comparación. Dispositivos Lógicos Programables 5 Práctica 2 Comparador de Magnitud 3. 4. 5. El alumno generará el archivo binario COMP4x4.BIN empleando el software del programador SuperPro, para ello deberá insertar la tabla de 256 valores que representan las combinaciones posibles del comparador. El alumno realizará la simulación del circuito del procedimiento experimental considerando la figura 2.2 siguiendo los pasos del desarrollo. Considere emplear el circuito de memoria 2732 en sustitución del circuito AT28C16 de la práctica, considerando que tiene una terminal de direcciones extra. Esta sustitución es necesaria debido a que el simulador no tiene un modelo de simulación para la memoria AT28C16. Entregar los resultados de la simulación de forma impresa al profesor al inicio de la sesión de laboratorio. Material 1 Memoria AT28C16 3 Resistencias de 330 Ω 1 Barra de 8 leds ó en su defecto 3 leds individuales. Equipo 1 Fuente de voltaje de CD. 1 Multímetro 1 Programador Universal 1 Protoboard Procedimiento Experimental 1. 2. 3. 4. Generar la tabla de valores en el editor de buffer del software SuperPro. Salvar el buffer en formato binario seleccionando la pestaña de Archivo/Guardar y asignando el nombre COMP4x4, designe la carpeta de almacenamiento que desee. Programe la memoria AT28C16 con archivo COMP4x4.BIN Implemente el circuito de la figura 2.2. Fig 2.2 Comparador de Magnitud de 4 bits 5. 6. Compruebe la función de comparación del circuito proponiendo una tabla de 8 valores para el dato A y 8 valores para el dato B. Llene la tabla 2.1 con los valores obtenidos del circuito y verifique que la operación se está realizando correctamente. Dispositivos Lógicos Programables 6 Práctica 2 Comparador de Magnitud Dato A Dato B Función Tabla 2.1 Cuestionario 1. 2. Obtenga las funciones de Boole para cada una de las 3 salidas del circuito, emplee mapas de Karnaugh. Determine de la hoja técnica el tiempo requerido para realizar la comparación. Dispositivos Lógicos Programables 7 Práctica 3 Contador Digital de la Sucesión de Fibonacci Laboratorio de Dispositivos Lógicos Programables 1. 2. Práctica 3 Contador Digital de la Sucesión de Fibonacci Tema: 2.3 Memorias de solo lectura (ROM’s). Objetivos Comprender los conceptos de diseño para circuitos secuenciales implementados sobre dispositivos lógicos programables. Implementar un contador programable sobre una memoria EEPROM que muestre secuencialmente los 13 primeros dígitos que forman la sucesión de Fibonacci. Introducción En matemáticas, la sucesión de Fibonacci es la sucesión infinita de números naturales: 1, 1, 2, 3, 5, 8, 13, 21, 34, 55, 89, 144 ,233, 377, … La sucesión comienza con los números 1 y 1, y a partir de estos, cada término subsecuente es la suma de los dos anteriores siguiendo la regla: xn = xn-1 + xn-2 A los elementos de esta sucesión se les llama números de Fibonacci. Esta sucesión fue descrita en Europa por Leonardo de Pisa, matemático italiano del siglo XIII también conocido como Fibonacci. Tiene numerosas aplicaciones en ciencias de la computación, matemáticas y teoría de juegos. También aparece en configuraciones biológicas, como por ejemplo en las ramas de los árboles, en la disposición de las hojas en el tallo, en la flora de la alcachofa y en el arreglo de un cono. Fig. 3.1 Sucesión de Fibonacci en forma geométrica y en la naturaleza. En esta práctica se realizará un contador binario programable que muestre los primeros 13 valores de la serie de Fibonacci e intercalando entre ellos el número cero para poderlos visualizar en forma correcta en una serie de 8 leds. Este contador programable puede realizarse si implementamos una máquina secuencial con un dispositivo lógico programable como una EEPROM. Dispositivos Lógicos Programables 8 Práctica 3 Contador Digital de la Sucesión de Fibonacci Lo que se requiere es que un contador binario natural vaya incrementando el valor de las direcciones de entrada de la memoria para que se produzca un recorrido por los valores almacenados en las localidades internas y se vuelva a repetir de forma infinita. La máquina secuencial implementada de esta manera, es capaz de trasladarse a través de todos los estados almacenados sin utilizar los flip flops típicos de los sistemas secuenciales, puesto que no se requiere la utilización de las tablas de estado ni de los análisis de excitaciones. En esta práctica se realizará el conteo desde el número 1 hasta el 233 de la sucesión de Fibonacci debido a que como la salida está restringida a 8 bits, no podemos alcanzar el siguiente valor que sería 377. Hay que hacer notar que este circuito no es un generador de la sucesión puesto que no ejecuta el algoritmo de cálculo que define a la sucesión sino solo se limita a mostrar los primeros 13 valores de la sucesión empleando una máquina secuencial. Fig.3.2 Diagrama de estados del contador La tabla constará de 23 estados que serán recorridos secuencialmente a una frecuencia definida por el reloj de un contador de 5 bits que se deberá resetear al llegar a 26 cuentas. El valor cero insertado de forma artificial es simplemente para visualizar de forma más cómoda la secuencia. Hay que indicar que la inserción del cero no sería posible si se realizara el circuito con lógica digital secuencial discreta puesto que no puede tenerse un conteo que pasa múltiples veces por el mismo valor 0 en diferentes puntos del diagrama ya que esto rompe con la secuencia lógica, pues no se pueden definir estados siguientes diferentes para las mismas condiciones de estado anterior. El circuito integrado que usaremos como contador de 5 bits será un 74LS393 como el mostrado en la figura 3.3. Dispositivos Lógicos Programables 9 Práctica 3 Contador Digital de la Sucesión de Fibonacci Fig 3.3 Circuito contador doble de 4 bits 74LS393 Actividades previas a la realización de la práctica 1. 2. 3. 4. El alumno deberá realizar la lectura de la práctica. El alumno generará el archivo binario FIBONACI.BIN empleando el software del programador SuperPro, para ello deberá insertar la tabla de 26 valores que representan a la máquina de estados. El alumno realizará la simulación de los circuitos del procedimiento experimental considerando la figura 3.4 siguiendo los pasos del desarrollo. Considere emplear el circuito de memoria 2732 en sustitución del circuito AT28C16 de la práctica, considerando que tiene una terminal de direcciones extra. Esta sustitución es necesaria debido a que el simulador no tiene un modelo de simulación para la memoria AT28C16. Entregar los resultados de la simulación de forma impresa al profesor al inicio de la sesión de laboratorio. Material 1 Memoria AT28C16 1 Circuito integrado 74LS393 1 Circuito integrado 74LS08 8 Resistencias de 330 Ω 1 Barra de 8 leds ó en su defecto 8 leds individuales. Equipo 1 Fuente de voltaje de CD. 1 Multímetro 1 Programador Universal 1 Protoboard Procedimiento Experimental 1. 2. 3. 4. 5. 6. 7. Generar la tabla de valores en el editor de buffer del software SuperPro. Salvar el buffer en formato binario seleccionando la pestaña de Archivo/Guardar y asignando el nombre FIBONACI, designe la carpeta de almacenamiento que desee. Programe la memoria AT28C16 con archivo FIBONACI.BIN Implemente el circuito de la figura 3.4. Compruebe que el conteo se realiza de forma correcta con la inserción de los ceros entre cada valor. Diseñe dos máquinas secuenciales, una que cuente en código gray ascendente de 5 bits y un contador descendente binario natural de 5 bits, se debe poder seleccionar cuál de las 2 máquinas funciona. Implemente su diseño y pruebe que funcionen ambas máquinas. Dispositivos Lógicos Programables 10 Práctica 3 Contador Digital de la Sucesión de Fibonacci Fig. 3.4 Contador de la Secuencia de Fibonacci Cuestionario 1. 2. Analice y explique la función que realiza el contador y las compuertas AND, indicando en forma binaria su comportamiento. Investigue y comente acerca de las siguientes características de los dispositivos lógicos programables Proceso de diseño de los sistemas que los contienen Recursos en los PLD’s Seguridad. Confiabilidad. Costo. Flexibilidad Dispositivos Lógicos Programables 11 Práctica 4 Display Alfanumérico 7x5 con 2 máquinas secuenciales 1. 2. Laboratorio de Dispositivos Lógicos Programables Práctica # 4 Display Alfanumérico 7x5 con 2 máquinas secuenciales Tema: 2.3. Memorias de solo lectura (ROM’s). Objetivos Implementar 2 máquinas secuenciales individuales que controlen el desplegado de símbolos alfanuméricos en un display de 7x5 leds. Comprobar el funcionamiento de un registro de corrimiento implementado sobre una EEPROM. Implementar la sincronización del envío de datos y registro de corrimiento al display. Introducción En esta práctica realizaremos la activación de un display alfanumérico matricial de 35 leds, arreglados en 7 renglones y 5 columnas. Figura 4.1 Display de 7 renglones y 5 columnas Estos displays están construídos de tal forma que los leds de un renglón comparten la misma línea de conexión y asimismo los leds de una columna comparten una sola línea lo cual reduce el número de terminales para la activación de los 35 leds que de otra manera requerirían 70 terminales para su conexión individual. Cada uno de los leds se enciende cuando se aplica un voltaje de 5V en la columna y 0V en el renglón para displays de ánodo común y cuando se aplica 0V en la columna y 5V en el renglón para displays de cátodo común. Figura 4.2 Disposición de leds en el display 7 x 5 El display que utilizaremos en la práctica es de ánodo común por lo que enciende con 5V en sus columnas y con asignaciones de 0V en aquellos leds que deseamos encender. Diseño de Sistemas Digitales empleando Dispositivos Lógicos Programables PLDs 12 Práctica 4 Display Alfanumérico 7x5 con 2 máquinas secuenciales Debido a que el encendido del display se realiza columna por columa, se requiere construír un circuito de corrimiento de 5 bits que proporcione voltaje de 5V a cada una de las columnas en forma secuencial y que al mismo tiempo coincida con un cero en la posición del renglón del led que deseamos encender. El sistema deberá contar con 2 memorias, una que sirva para generar el registro de corrimiento y otra para almacenar los datos que vamos a desplegar en conjuntos de 5 datos de 7 bits. Los datos que deberán almacenarse en la memoria de datos, se muestran en la figura 4.3. Figura 4.3 Caracteres a desplegar Estos caracteres se deben almacenar a partir de la localidad cero de la memoria de datos y cubriendo 5 localidades, cada letra se seleccionará a partir de 4 bits de control que definen una localidad de memoria a partir de la cual se despliega cada una de las máquinas de estado. Los datos almacenados en la memoria solo emplean los 7 bits menos significativos y el octavo bit se cargará con cero. Actividades previas a la realización de la práctica 1. 2. 3. 4. El alumno deberá realizar la lectura de la práctica. El alumno realizará la programación de la primera memoria AT28C16 con con los datos del registro de corrimiento mostrados en la figura 4.5 y la segunda memoria se debe programar con la tabla de datos correspondiente a los caracteres, mostrada en la figura 4.6 Como la tabla solo contiene 12 caracteres y se puede controlar la exhibición de 16, el alumno deberá generar 4 caracteres adicionales e incluirlos en la programación. El alumno realizará la simulación de los circuitos del procedimiento experimental considerando la figura 4.4 siguiendo los pasos del desarrollo. Considere emplear el circuito de memoria 2732 en sustitución del circuito AT28C16 de la práctica, considerando que tiene una terminal de direcciones extra. Esta Diseño de Sistemas Digitales empleando Dispositivos Lógicos Programables PLDs 13 Práctica 4 Display Alfanumérico 7x5 con 2 máquinas secuenciales 5. sustitución es necesaria debido a que el simulador no tiene un modelo de simulación para la memoria AT28C16. Entregar los resultados de la simulación de forma impresa al profesor al inicio de la sesión de laboratorio. Material 2 Memoria AT28C16 1 74LS393 1 74LS08 1 Display de matriz de leds de 7 x 5 ánodo común Equipo 1 Fuente de voltaje de CD. 1 Multímetro 1 Programador Universal 1 Protoboard Procedimiento Experimental 1. Implemente el circuito de la figura 4.4. Figura 4.4 2. Programe la memoria 2716 que contendrá el registro de corrimiento con la tabla de la figura 4.5 Figura 4.5 Registro de corrimiento Diseño de Sistemas Digitales empleando Dispositivos Lógicos Programables PLDs 14 Práctica 4 Display Alfanumérico 7x5 con 2 máquinas secuenciales 3. Programe la memoria 2716 que contendrá la tabla de datos de acuerdo a la figura 4.6 Figura 4.6 Tabla de datos para 12 caracteres. 4. 5. 6. 7. 8. 9. Con una señal de reloj de 1Hz compruebe que se genera el registro de corrimiento y se produce el encendido de cada una de las columnas del circuito para una entrada de selección 0010. Incremente la frecuencia de reloj y verifique que la visualización se realiza cada vez más rápido. Aumente la frecuencia de reloj hasta que ya no pueda observarse el parpadeo de las columnas al apagarse, anote el valor de la frecuencia que produce este efecto. Compruebe que se pueden visualizar los 4 caracteres diseñados por el alumno. Diseñe una animación que muestre un asterisco que gire utilizando la siguiente secuencia de cuatro etapas y repitiéndose de forma constante. Implemente el circuito y pruébelo para mostrar la animación en el display. Cuestionario 1. 2. 3. 4. Cuál es la función de la compuerta AND en el sistema. Indique cual es la frecuencia mínima para que se produzca este efecto y porque se puede ver el carácter completo como si el encendido fuera simultáneo. Incluya las gráficas y valores para los 4 caracteres diseñados. Incluya el diseño del circuito de animación. Diseño de Sistemas Digitales empleando Dispositivos Lógicos Programables PLDs 15 Práctica 5 Decodificador de Teclado con GAL y algebra de Boole 1. 2. Laboratorio de Dispositivos Lógicos Programables Práctica 5 Decodificador de Teclado con GAL y algebra de Boole Tema: 2.6. Arreglos lógicos genéricos (GAL’s). Objetivos Implementar un decodificador de teclado matricial telefónico de 12 teclas. Obtener la representación en algebra de Boole de la tabla de verdad del decodificador Implementar las ecuaciones de Boole dentro de un dispositivo GAL22V10 Introducción En esta práctica realizaremos la decodificación de un teclado matricial de 12 teclas utilizado para la marcación en los teléfonos como el mostrado en la figura 5.1. Este teclado presenta un conjunto de 12 teclas arregladas en un formato de matriz que activa un renglón y una columna en correspondencia con la tecla presionada. Figura 5.1 Existen varias formas de decodificarlo, una de ellas utiliza un registro de corrimiento que activa los renglones en forma consecutiva del renglón 1 al 4, repitiendo el proceso una y otra vez a una frecuencia elevada, analizando el valor que presentan las columnas y haciendo el análisis de que renglón y columna están activas en el instante de tiempo en que se presiona la tecla, se puede por lo tanto asignar el código correspondiente en binario u otro código, de cada una de las teclas. En esta práctica emplearemos un método de decodificación que aprovecha una terminal del teclado que es común a todas las teclas y por lo tanto no requiere del registro de corrimiento externo. Este proceso de decodificación es totalmente estático ya que se emplean 7 resistencias conectadas a la fuente de alimentación y donde la tecla presionada funciona como un switch conectado a tierra y genera un cero lógico tanto en el renglón como en la columna donde está posicionada la tecla. Diseño de Sistemas Digitales empleando Dispositivos Lógicos Programables PLDs 16 Práctica 5 Decodificador de Teclado con GAL y algebra de Boole Salidas hacia la GAL R39 5V 1k 1k 1k 1k 1k 1k R40 R41 R42 R43 R44 R45 Gris 1 2 3 4 5 6 Azul 7 8 9 Amarillo * 0 # 1k Violeta Cafe Naranja Rojo Verde 0 Figura 5.2 Decodificación estática del teclado En esta práctica se requiere el planteamiento de las tablas de verdad para las 7 entradas, 3 columnas y 4 renglones y las 5 salidas, código binario de 4 bits para identificar 12 teclas y además 1 salida adicional para indicar que una tecla se ha presionado y por lo tanto el código de salida es válido, esto es necesario porque no podría distinguirse entre el código de salida 0000 debido a que ninguna tecla está presionada y el código 0000 debido a la tecla 0 que es un código válido. La asociación de códigos para cada tecla se muestra en la tabla 5.1, observe que el código de validez de código (V) esta activo en 1 solo para las 12 combinaciones mostradas de las 128 posibles y por lo tanto los 116 restantes deben tener el bit V = 0. Tecla 1 2 3 4 5 6 7 8 9 * 0 # Renglones A 0 1 1 0 1 1 0 1 1 0 1 1 BC 11 01 10 11 01 10 11 01 10 11 01 10 Columnas D 0 0 0 1 1 1 1 1 1 1 1 1 E 1 1 1 0 0 0 1 1 1 1 1 1 FG 11 11 11 11 11 11 01 01 01 10 10 10 Bit de código Válido V 1 1 1 1 1 1 1 1 1 1 1 1 Código de tecla WXYZ 0001 0010 0011 0100 0101 0110 0111 1000 1001 1010 0000 1011 Tabla 5.1 Actividades previas a la realización de la práctica 1. 2. 3. El alumno deberá realizar la lectura de la práctica. El alumno obtendrá las 5 ecuaciones de Boole que representan a cada una de las variables de salida de la tabla 5.1 (V, W, X, Y y Z) y comprobará que concuerdan con las ecuaciones del desarrollo. El alumno creará un proyecto en el programa ISPLEVER para insertar las ecuaciones de Boole. Diseño de Sistemas Digitales empleando Dispositivos Lógicos Programables PLDs 17 Práctica 5 Decodificador de Teclado con GAL y algebra de Boole 4. 5. 6. El alumno generará el archivo P5_PLDs.JED que se empleará para programar a la GAL. El alumno realizará la simulación de los circuitos del procedimiento experimental considerando la figura 5.3 siguiendo los pasos del desarrollo. El teclado deberá ser simulado con entradas individuales ya que el teclado del simulador solo puede ser decodificado en forma dinámica con registros de corrimiento. Entregar los resultados de la simulación de forma impresa al profesor al inicio de la sesión de laboratorio. Material 1 GAL22V10D 1 Teclado telefónico de 12 teclas. 4 Resistencias de 330 Ω 1 Barra de 8 leds ó en su defecto 5 leds individuales. Equipo 1 Fuente de voltaje de CD. 1 Multímetro 1 Programador Universal 1 Protoboard Procedimiento Experimental 1. Ejecute el software ISPLEVER. Figura 5.3 2. Cree un proyecto nuevo denominado P5_PLDs con lenguaje VHDL y en la carpeta que usted seleccione. Figura 5.4 3. Seleccione el tipo de dispositivo activando la casilla de: Show Obsolete Devices Seleccione Family: GAL Device Seleccione Device: GAL22V10D Seleccione Package Type: 24 PDIP Todos los parámetros restantes deben dejarse con su opción default. Considere la figura 5.5 para definir estas opciones Finalice el proceso para crear el proyecto. Diseño de Sistemas Digitales empleando Dispositivos Lógicos Programables PLDs 18 Práctica 5 Decodificador de Teclado con GAL y algebra de Boole Figura 5.5 4. Cree un archivo fuente nuevo y seleccione un tipo de proyecto VHDL Module Figura 5.6 5. Defina las variables de entrada y salida del sistema así como la indicación de si son entradas o salidas, según se muestra en la figura 5.7. Figura 5.7 6. 7. Figura 5.8 A partir de la información insertada se crea el archivo mostrado en la figura 5.8. Complete la información mostrada en la figura 5.9 para incluir la definición de terminales y las funciones de Boole para las variables V, W, X, Y y Z. Diseño de Sistemas Digitales empleando Dispositivos Lógicos Programables PLDs 19 Práctica 5 Decodificador de Teclado con GAL y algebra de Boole 8. Figura 5.9 Compile el proyecto con la opción JEDEC File como se muestra en la figura 5.10, obtenga el archivo P5_PLDs.JED y programe la GAL con dicho archivo. Figura 5.10 9. Implemente el circuito mostrado en la figura 5.11 considerando los cables del teclado mostrados en la figura 5.2. 10. Compruebe el código de cada una de las teclas y el bit de validez de código. Diseño de Sistemas Digitales empleando Dispositivos Lógicos Programables PLDs 20 Práctica 5 Decodificador de Teclado con GAL y algebra de Boole Figura 5.11 Cuestionario 1. 2. 3. Describa la función que realiza el comando LOC en el programa en VHDL. Imprima la hoja técnica de la GAL22V10D y describa las características y funcionalidad de las terminales de entrada y salida. Describa la característica de los tiempos de acceso y compárela con los tiempos de acceso de la implementación discreta considerando las funciones de Boole obtenidas en las actividades previas. Diseño de Sistemas Digitales empleando Dispositivos Lógicos Programables PLDs 21 Práctica 6 Implementación de Tablas de Verdad con GALs Laboratorio de Dispositivos Lógicos Programables 1. 2. Práctica 6 Implementación de Tablas de Verdad con GALs Tema: 2.6. Arreglos lógicos genéricos (GAL’s). Objetivos Implementar tablas de verdad de circuitos lógicos dentro de un dispositivo lógico programable considerando lenguaje VHDL. Utilizar la característica de concurrencia del lenguaje VHDL para la representación de una tabla de verdad. Introducción En esta práctica implementaremos las tablas de verdad de 3 circuitos lógicos empleando para ello la característica de concurrencia que tiene el lenguaje VHDL, el cual no ejecuta las instrucciones de forma secuencial sino de forma concurrente y cualquier cambio en las variables de entrada se refleja inmediatamente en las variables de salida puesto que el sistema funciona como lo hace un circuito verdadero, ya que este sistema no depende de la programación como lo hacen los microprocesadores. El primer circuito es un Codificador de código binario a un código de 7 segmentos que tiene una tabla de verdad como la mostrada en la figura 6.1. Código Binario ABCD 0000 0001 0010 0011 0100 0101 0110 0111 1000 1001 1010 1011 1100 1101 1110 1111 Código de 7 segmentos abcdefg 1111110 0110000 1101101 1111001 0110011 1011011 1011111 1110000 1111111 1111011 1110111 0011111 1001110 0111101 1001111 1000111 Figura 6.1 Tabla de verdad del codificador binario a 7 segmentos Diseño de Sistemas Digitales empleando Dispositivos Lógicos Programables PLDs 22 Práctica 6 Implementación de Tablas de Verdad con GALs El cual se implementará a partir de la función WITH … SELECT del lenguaje VHDL, la cual permite definir la salida en función del valor de una variable de selección. En las variables de entrada se empleará el método de definición de vector lógico estándar, para poderlas manipular en forma de bloque. En el segundo circuito se implementará un Codificador de BCD a 7 segmentos considerando la variante de WITH … SELECT empleando la palabra OTHERS que define a todas las combinaciones de entrada que no han sido empleadas dentro de la tabla, sin importar si están en orden o no. De las 16 combinaciones posibles para 4 bits de entrada, solo se emplearán las 10 posibles para código BCD y las 6 restantes se agrupan en la declaración OTHERS. Para la tercera parte de la práctica emularemos el comportamiento de un circuito 74138, Codificador/Demultiplexor de 1 a 8, como el que se muestra en la figura 6.2 Figura 6.2 Circuito 74LS138 Este circuito integrado tiene 8 salidas (Y7 a Y0), 3 selectores de canal (C, B y A) y 3 habilitadores (G2A, G2B y G1), como se muestra en las figuras 6.2 y 6.3. Figura 6.3 Puede emularse el comportamiento del circuito 74LS138 empleando un dispositivo lógico programable GAL22V10D identificando solamente la tabla de verdad de la figura 6.4 e implementando dichas relaciones a través del lenguaje VHDL. Diseño de Sistemas Digitales empleando Dispositivos Lógicos Programables PLDs 23 Práctica 6 Implementación de Tablas de Verdad con GALs Figura 6.4 Tabla de verdad del circuito 74LS138 Para la implementación de este circuito emplearemos la función WHEN … ELSE en la cual se incluirán dos condiciones de selección y una asignación de salida. También se utilizará la definición de variables intermedias para facilitar la manipulación de los datos, estas se definirán a partir de la palabra clave SIGNAL. SIGNAL SELECTORES : std_logic_vector (2 DOWNTO 0); SIGNAL HABILITADORES : std_logic_vector (2 DOWNTO 0); El último elemento a utilizar será el comando de concatenación (&) para trabajar las señales de entrada en forma de vector. SELECTORES <= A & B & C; HABILITADORES <= G1 & G2A & G2B; Actividades previas a la realización de la práctica 1. 2. 3. 4. 5. 6. El alumno deberá realizar la lectura de la práctica. El alumno generará el archivo binario P6_Binario.JED empleando el software ISPLever, para el codificador binario a 7 segmentos de la figura 6.6. El alumno generará el archivo binario P6_BCD.JED empleando el software ISPLever, para el codificador BCD a 7 segmentos de la figura 6.6. El alumno generará el archivo binario P6_74138.JED empleando el software ISPLever, para la emulación del circuito 74LS138 de la figura 6.9 El alumno realizará la simulación de los circuitos del procedimiento experimental siguiendo los pasos del desarrollo. Entregar los resultados de la simulación de forma impresa al profesor al inicio de la sesión de laboratorio. Material 1 Circuito GAL22V10D 1 Display de 7 segmentos cátodo común 8 Resistencias de 330 Ω 1 Barra de 8 leds ó en su defecto 8 leds individuales. Diseño de Sistemas Digitales empleando Dispositivos Lógicos Programables PLDs 24 Práctica 6 Implementación de Tablas de Verdad con GALs Equipo 1 Fuente de voltaje de CD. 1 Multímetro 1 Programador Universal 1 Protoboard Procedimiento Experimental 1. Cree un proyecto en el software ISPLever denominado P6_Binario y genere el archivo P6_Binario.JED utilizando las instrucciones descritas en el archivo VHDL de la figura 6.5. Figura 6.5 Archivo VHDL para el codificador binario a 7 segmentos 2. Implemente el circuito de la figura 6.6. Figura 6.6 Codificador binario a 7 segmentos Diseño de Sistemas Digitales empleando Dispositivos Lógicos Programables PLDs 25 Práctica 6 Implementación de Tablas de Verdad con GALs 3. 4. Programe la GAL con el archivo P6_Binario.JED y compruebe el correcto funcionamiento de las 16 combinaciones del codificador. Cree un proyecto en el software ISPLever denominado P6_BCD y genere el archivo P6_BCD.JED utilizando las instrucciones descritas en el archivo VHDL de la figura 6.7. Figura 6.7 Codificador de BCD a 7 segmentos. 5. 6. Empleando el circuito de la figura 6.6, reprograme la GAL para realizar la comprobación del codificador BCD a 7 segmentos en sus primeras 10 combinaciones y las 6 combinaciones restantes sin activación del display. Cree un proyecto en el software ISPLever denominado P6_74138 y genere el archivo P6_74138.JED utilizando las instrucciones descritas en el archivo VHDL de la figura 6.8. Figura 6.8 Archivo VHDL para circuito 74138 (1ª parte) Diseño de Sistemas Digitales empleando Dispositivos Lógicos Programables PLDs 26 Práctica 6 Implementación de Tablas de Verdad con GALs Figura 6.8 Archivo VHDL para circuito 74138 (2ª parte) 7. Implemente el circuito de la figura 6.9. Figura 6.9 Emulador de circuito 74138 8. Programe la GAL con el archivo P6_74138.JED y compruebe el correcto funcionamiento de la tabla de verdad del circuito 74138. Cuestionario 1. 2. 3. Describa el significado de las siglas VHDL. Describa las características del lenguaje VHDL. Investigue las diferencias y similitudes entre una declaración de señal de entrada bit y una señal de entrada std_logic. Diseño de Sistemas Digitales empleando Dispositivos Lógicos Programables PLDs 27 Práctica 7 Control de Potencia con Flip Flops en dispositivos PLD 1. 2. Laboratorio de Dispositivos Lógicos Programables Práctica 7 Control de Potencia con Flip Flops en dispositivos PLD Tema: 2.6. Arreglos lógicos genéricos (GAL’s). Objetivos Comprender la utilización de las extensiones empleadas en las macroceldas de los PLD´s. Comprobar el procedimiento para asignar señales o funciones a las extensiones de los flip flops. Realizar el control de potencia de corriente alterna utilizando al PLD como elemento de control. Introducción El desarrollo de la tecnología de fabricación de los PLD´s permitió emplear elementos cada vez más sofisticados tanto en sus entradas como en sus salidas y eso derivó en la creación de sistemas electrónicos que permitan el almacenamiento, el encendido, el apagado, el cambio de polaridad y la multiplexación de las señales de salida. Estos elementos electrónicos que mejoran la funcionalidad de los PLD y su estructura básica, están concentrados en un elemento llamado macrocelda de salida lógica (Output Logic Macrocell) o OLMC. Figura 7.1 OLMC Output Logic Macrocell de la GAL22V10D En la OLMC del circuito GAL22V10D se puede observar que cada salida de la OR de minitérminos puede asociarse con un Flip Flop tipo D que tiene: Señal de reloj compartida que se distribuye a partir de la terminal número 1, la cual permite realizar diseños síncronos. Salidas 𝑄 y 𝑄̅ que permite obtener en la salida la polaridad normal y la negada. Una señal de control denominada AR (Asynchronous Reset) o Reset Asíncrono que produce que la salida Q vaya a bajo inmediatamente después de aplicarla sin intervención o relación con el reloj aplicado al flip flop. Diseño de Sistemas Digitales empleando Dispositivos Lógicos Programables PLDs 28 Práctica 7 Control de Potencia con Flip Flops en dispositivos PLD Una señal de control denominada SP (Synchronous Preset) o Preset Síncrono que produce que la salida Q vaya a alto en sincronía con el pulso de subida del reloj. Una señal de control que permite habilitar o deshabilitar la salida de la señal denominada OE (Output Enable) o Habilitador de Salida. Cada una de estas extensiones, a excepción del reloj pueden ser controlados por una señal de entrada al PLD o por una función lógica, siempre y cuando se haga una asociación de la señal con la extensión indicada a través de un punto y el nombre de la extensión al final del nombre de la señal. En esta práctica se aplicarán señales externas a cada una de las señales de control y se comprobará el funcionamiento del flip flop correspondiente en forma lógica como se muestra en la figura 7.2. salida.D = dato; salida.AR = !clear; salida.SP = !set; salida.OE = enable; Figura 7.2 asignación de señales a extensiones del Flip Flop La señal de salida de la GAL se aplicará a una interfaz de potencia para controlar el encendido y apagado de la carga con un voltaje de alterna de 127 V. Esta interfaz de potencia se realizará con un circuito optoaislador MOC 3010 que contiene un led infrarrojo y un triac con compuerta infrarroja que tiene como inconveniente el manejo de corrientes reducidas (100mA) aproximadamente, en la figura 7.3 se muestra el diagrama de terminales y el diagrama lógico. Debido a la baja corriente de salida se deberá utilizar un segundo TRIAC de corriente elevada para controlar a la carga. Figura 7.3 Opto Triac MOC 3010 El triac que controlará la potencia entregada a la carga será un TIC206D que puede manipular una corriente de 4 A. con un voltaje de hasta 400V, aunque se pueden emplear triacs de mayor corriente y voltaje. Figura 7.4 Triac TIC206D Actividades previas a la realización de la práctica 1. 2. 3. El alumno deberá realizar la lectura de la práctica. El alumno realizará la simulación del circuito del procedimiento experimental considerando la figura 7.6 siguiendo los pasos del desarrollo, debe omitirse la simulación para el dispositivo Opto aislador MOC3011 pues no produce los resultados reales del circuito y deberá ser probado solo en forma práctica. Entregar los resultados de la simulación de forma impresa al profesor al inicio de la sesión de laboratorio. Diseño de Sistemas Digitales empleando Dispositivos Lógicos Programables PLDs 29 Práctica 7 Control de Potencia con Flip Flops en dispositivos PLD Material 1 GAL22V10D 2 Resistencias de 330 Ω 1 TRIAC TIC206D 1 MOC3010 1 Foco incandescente 1 Cable de alimentación eléctrica 2 polos 1 Clavija Equipo 1 Fuente de voltaje de CD. 1 Multímetro 1 Programador Universal 1 Protoboard 1 Generador de funciones Procedimiento Experimental 1. El alumno creará el proyecto P7_MOC3010.PLD en el software Wincupl de acuerdo a la figura 7.5. Figura 7.5 Proyecto P7_MOC3010 2. 3. 4. 5. 6. 7. 8. Generar el archivo P7_MOC3010.JED. Programar la GAL22V10 con el archivo JED. Implementar el circuito de la figura 7.6. Calibrar el generador de funciones con una señal cuadrada de niveles TTL y una frecuencia de 1 Hz. Considere que la alimentación del foco es de 127 V de c.a. de la línea y que deberá tomar todas las precauciones necesarias para evitar una descarga eléctrica a algún miembro del equipo o a la fuente de voltaje. La clavija deberá instalarse en el cable y las otras 2 puntas deberán conectarse al circuito. Considere que el circuito del lado derecho de la figura 7.6 no está conectado a tierra. Diseño de Sistemas Digitales empleando Dispositivos Lógicos Programables PLDs 30 Práctica 7 Control de Potencia con Flip Flops en dispositivos PLD Figura 7.6 Compruebe la posición de las conexiones y evite que las terminales del cable de alimentación toquen alguna otra parte del circuito. 10. Compruebe el funcionamiento del reloj y el funcionamiento de las 4 terminales restantes que controlan al Flip Flop D. 11. Compruebe que el foco se encienda y apague de acuerdo a la salida de la GAL. 9. Cuestionario 1. 2. 3. Investigue las condiciones de funcionamiento del MOC 3010 con respecto a las corrientes y voltajes que se requieren para activar al led infrarrojo de entrada y las capacidades de corriente y voltaje del TRIAC de salida. Qué ventajas y desventajas tiene el controlar cargas de corriente alterna empleando rectificadores de estado sólido en lugar de relevadores. Investigue las características de los dispositivos denominados SCR y TRIAC que se emplean para el control de potencia alterna. Diseño de Sistemas Digitales empleando Dispositivos Lógicos Programables PLDs 31