TRABAJO 1. UNIDAD IV. UNIDAD DE CONTROL Objetivo. Trabajar

Anuncio

ELECTRÓNICA DIGITAL

1

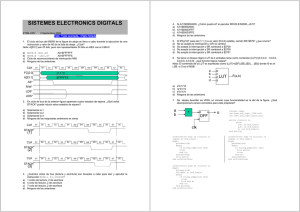

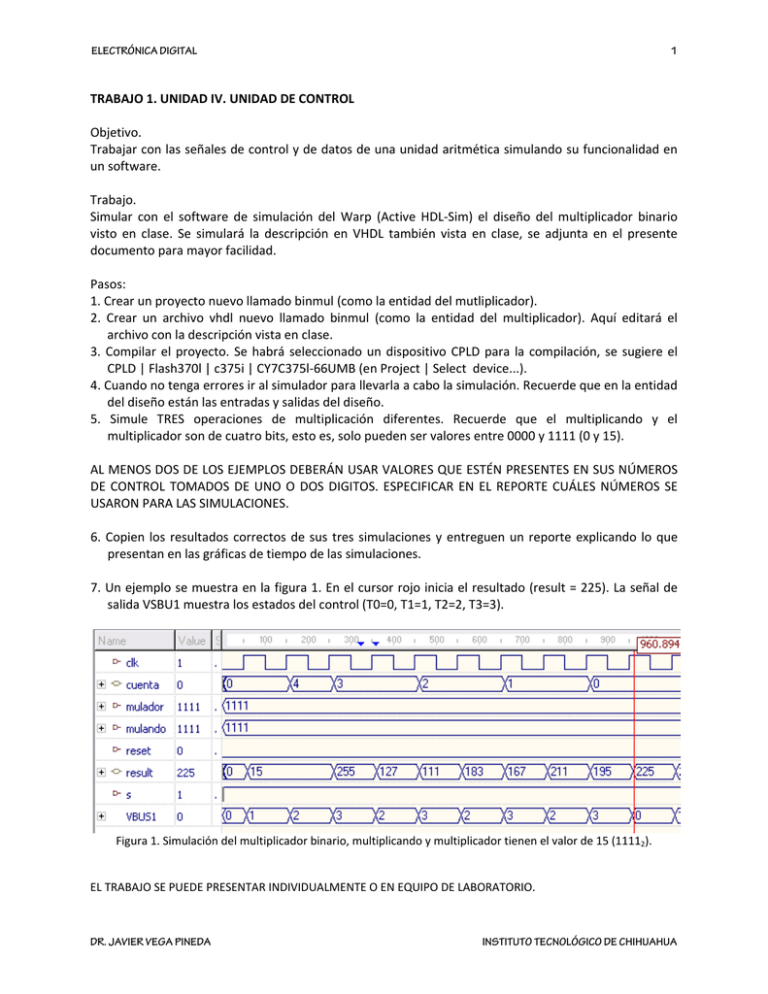

TRABAJO 1. UNIDAD IV. UNIDAD DE CONTROL Objetivo. Trabajar con las señales de control y de datos de una unidad aritmética simulando su funcionalidad en un software. Trabajo. Simular con el software de simulación del Warp (Active HDL‐Sim) el diseño del multiplicador binario visto en clase. Se simulará la descripción en VHDL también vista en clase, se adjunta en el presente documento para mayor facilidad. Pasos: 1. Crear un proyecto nuevo llamado binmul (como la entidad del mutliplicador). 2. Crear un archivo vhdl nuevo llamado binmul (como la entidad del multiplicador). Aquí editará el archivo con la descripción vista en clase. 3. Compilar el proyecto. Se habrá seleccionado un dispositivo CPLD para la compilación, se sugiere el CPLD | Flash370l | c375i | CY7C375l‐66UMB (en Project | Select device...). 4. Cuando no tenga errores ir al simulador para llevarla a cabo la simulación. Recuerde que en la entidad del diseño están las entradas y salidas del diseño. 5. Simule TRES operaciones de multiplicación diferentes. Recuerde que el multiplicando y el multiplicador son de cuatro bits, esto es, solo pueden ser valores entre 0000 y 1111 (0 y 15). AL MENOS DOS DE LOS EJEMPLOS DEBERÁN USAR VALORES QUE ESTÉN PRESENTES EN SUS NÚMEROS DE CONTROL TOMADOS DE UNO O DOS DIGITOS. ESPECIFICAR EN EL REPORTE CUÁLES NÚMEROS SE USARON PARA LAS SIMULACIONES. 6. Copien los resultados correctos de sus tres simulaciones y entreguen un reporte explicando lo que presentan en las gráficas de tiempo de las simulaciones. 7. Un ejemplo se muestra en la figura 1. En el cursor rojo inicia el resultado (result = 225). La señal de salida VSBU1 muestra los estados del control (T0=0, T1=1, T2=2, T3=3). Figura 1. Simulación del multiplicador binario, multiplicando y multiplicador tienen el valor de 15 (11112). EL TRABAJO SE PUEDE PRESENTAR INDIVIDUALMENTE O EN EQUIPO DE LABORATORIO. DR. JAVIER VEGA PINEDA

INSTITUTO TECNOLÓGICO DE CHIHUAHUA

ELECTRÓNICA DIGITAL

2

CÓDIGO VHDL -- Multiplicador binario de 4 bits, libro de Morris Mano

-- Modificado por Javier Vega-Pineda (Octubre 2009)

library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_unsigned.all;

entity binmul is port(

clk, reset, s: in std_logic;

mulando, mulador: in std_logic_vector(3 downto 0);

--multiplicando y multiplicador

result: out std_logic_vector(7 downto 0); --resultado A y Q

cuenta: out std_logic_vector(2 downto 0));--contador P

end;

architecture elect_dig_2 of binmul is

type estado is (T0, T1, T2, T3);

signal edopte, edosgt: estado;

signal A: std_logic_vector(4 downto 0);

--A(4) = C

signal B, Q: std_logic_vector(3 downto 0);

--registros

signal P: std_logic_vector(2 downto 0);

--contador

signal Z: std_logic; --Carry out y bandera de cero del contador

begin

Z <= not(P(0) or P(1) or P(2));

result <= A(3 downto 0) & Q;

cuenta <= P;

registro_estado: process(clk, reset)

begin

if reset='1' then

edopte <= T0;

elsif (clk'event and clk = '1') then

edopte <= edosgt;

end if;

end process;

func_estado_sgte: process (s, Z, edopte)

begin

case edopte is

when T0 =>

if s='1' then

edosgt <= T1;

else

edosgt <= T0;

end if;

when T1 =>

edosgt <= T2;

when T2 =>

edosgt <= T3;

when T3 =>

DR. JAVIER VEGA PINEDA

INSTITUTO TECNOLÓGICO DE CHIHUAHUA

ELECTRÓNICA DIGITAL

3

if Z='1' then

edosgt <= T0;

else

edosgt <= T2;

end if;

end case;

end process;

func_datos: process(clk)

begin

if (clk'event and clk='1') then

case edopte is

when T0 =>

B<= mulando; Q <= mulador;

when T1 =>

A <= "00000"; P <="100";

when T2 =>

if Q(0)= '1' then

A <= A + ('0'& B);

end if;

P <= P - "001";

when T3 =>

Q <= A(0) & Q(3 downto 1);

A <= '0' & A(4 downto 1);

end case;

end if;

end process;

end;

ENTREGA DE SU REPORTE: LUNES 26 DE OCTUBRE EN CLASE DR. JAVIER VEGA PINEDA

INSTITUTO TECNOLÓGICO DE CHIHUAHUA