Implementación del algoritmo A5/1 (Cifrado de flujo de datos)

Anuncio

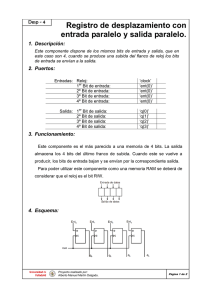

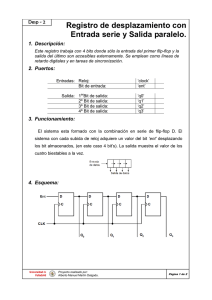

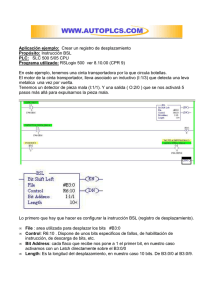

Implementación del algoritmo A5/1 (Cifrado de flujo de datos) Sabel Mercurio Hernández Rodríguez Sección de Computación CINVESTAV-IPN, México [email protected] México, D. F., a 23 de abril de 2004. Introducción Con la aparición de los primeros equipos informáticos, surgió la necesidad de poder interconectarlos de forma remota. Con el tiempo, y debido al aumento de la demanda de servicios de transmisión de datos cada vez más eficientes, los operadores de los distintos países comenzaron a instalar redes especialmente diseñadas para soportar este tipo de tráfico: Redes digitales por conmutación de paquetes, Redes digitales por conmutación de circuitos, Redes digitales de servicios integrados (Voz + datos); algo similar paso con la aparición de la telefonía celular. De las diferentes tecnologías de 2G (segunda generación) encontramos la aparición del GSM1, con este tipo de tecnología el panorama cambia completamente: se trata de una red digital. De las principales características de este tipo de red, es que permite identificar y distinguir, no sólo entre tráfico telefónico y de datos, sino que además diferencia entre llamadas de datos de distinta naturaleza (fax, datos, etc.), y en consecuencia darle el tratamiento adecuado a cada una de ellas. Además GSM con sus mecanismos de seguridad incorporados que incluyen, permiten por un lado la autenticación del terminal llamante así como la encriptación de la señalización e información transmitida (independientemente de que éste sea voz o datos) a través de la interfaz de radio. Objetivo Es importante mencionar que la autentificación y la encriptación de datos, son aspectos muy importantes a tomar en consideración, sobre todo cuando se trata de realizar una comunicación dentro de un canal abierto (donde cualquiera pueda interceptar las señales transmitidas); por lo que es indispensable contar con sistemas de seguridad que no permitan la decodificación de la información. El algoritmo A5/1 permite cubrir estas brechas de información, por lo que es importante realizar implementaciones (y sobretodo implementaciones en hardware) de este algoritmo para la encriptación de flujo de datos. 1 Global System for Mobile Communication: Sistema Global para Comunicaciones Remotas. Cifrado de flujo de datos basados en LFSR2 LFSR se emplean en distintos generadores de flujo de llaves por varias razones: 1. 2. 3. 4. LFSR se implementan más fácilmente en hardware; pueden generar secuencias con períodos muy largos3; pueden generar secuencias con excelentes propiedades estadísticas4; y debido a su estructura, pueden analizarse de manera analítica empleando técnicas algebraicas. Definición5 Un LFSR de longitude L contiene L pasos numerados 0; 1; … ; L - 1, cada uno capaz de almacenar un bit, teniendo un sola entrada y una sola salida; también cuenta con un reloj que controla el desplazamiento de los datos. Durante cada período de tiempo se realizan las siguientes operaciones: (i) (ii) (iii) el contenido del paso 0 es la salida que forma parte de la secuencia de salida; el contenido del paso i se desplaza al paso i – 1 para cada i, 1 ≤ i ≤ L - 1; y el nuevo contenido del paso L - 1 es el bit de retroalimentación sj el cual es calculado sumando los contenidos de los pasos anteriores modulo 2. Descripción del Algoritmo A5/1 El algoritmo A5/1 funciona como un cifrador de flujo de datos, y el flujo cifrado se consigue por medio de la operación xor de tres registros (controlado por medio de un reloj) con el flujo a cifrar. El bit que controla el reloj de cada uno de los registros, es un bit resultante de una función mayoritaria entre los tres bits centrales de cada registro (i.e. a cada paso habrá dos o tres registros en movimiento). La longitud de los tres registros ( R1 , R2 , R3 ) son 19, 22 y 23 bits respectivamente (por lo que la longitud de la llave es de 64 bits). Los polinomios que representan la función f(x) para cada uno de los registros son: f ( x1 ) = x 19 + x 18 + x 17 + x 14 + 1 f ( x 2 ) = x 22 + x 21 + 1 f ( x3 ) = x 23 + x 22 + x 21 + x 8 + 1 La figura 1 muestra el diagrama general de funcionamiento del algoritmo A5/1 2 Linear Feedback Shift Register: Registro de Desplazamiento Retroalimentado Linealmente. Esto con la finalidad de dificultar un ataque que quiera descrifrar el mensaje. 4 Tercer postulado de Golomb. 5 Definición tomada del libro: “Handbook of Applied Cryptography”, de A. Menezes, P. van Oorschot, and S. Vanstone, CRC Press, 1996. 3 19 14 C1 1 R1 9: bit de reloj ⊕ 22 f ( x1 ) = x 19 + x 18 + x 17 + x 14 + 1 C2 1 R2 Si ⊕ 11: bit de reloj ⊕ f ( x 2 ) = x 22 + x 21 + 1 23 C3 8 1 R3 11: bit de reloj ⊕ f ( x3 ) = x 23 + x 22 + x 21 + x 8 + 1 Descripción del Algoritmo A5 Figura 1 Implementación Primeramente se diseño un flip-flop de tipo D, con la finalidad de poder emplearlo para la construcción de los registros de corrimiento (r1, r2, r3). Tiene tres bits de entrada: reset (que permite reiniciar el circuito), clock (que es la señal de reloj para sincroniza el circuito), data_in (el dato a transferir); y tiene un salida data_out (que el la salida del flip-flop). El circuito resultante se puede observar en la figura 32 Figura 2. Donde las entradas: • data_in: Representa el bit de entrada. • clock: Es el reloj del sistema (permite la sincronización del sistema). • reset: Bit que reinicia el flip-flop. y la salida del flip-flop de tipo D: • data_out: Representa el bit de salida del flip-flop. Después se implementó un multiplexor de 4x1 (cuatro entradas una salida), el multiplexor nos permitirá dar mayor funcionalidad al flip-flops (resultando un registro tanto de corrimiento como registro de carga); se emplearán las siguientes entradas para determinar que funcionamiento tendrá el registro: • • • “00”: sin cambio (mantiene su estado acutal) “01”: carga en paralelo (carga dentro del registro el dato proporcionado por el usuario) “10”: desplazamiento a la derecha (función de corrimiento de bits) el circuito resultante se puede observar en la figura 3. Figura 3. Donde las entradas: • A, B, C: Representa los bits de entrada a seleccionar. • seleccion<1 : 0>: Son los bits que permiten seleccionar que entrada se desplegará en la salida. y la salida del multiplexor 4x1 es: • mux_out: Es el bit de salida del multiplexor. De los módulos principales se encuentran los 3 registros de desplazamiento (r1, r2. r3), para implementar cada registro se emplearon los circuitos anteriores y se conectarón en cascada para poder obtener el funcionamiento adecuado (ver figuras 4a, 4b). Cabe señalar que la salida de cada registro se obtiene mediante su respectiva función; por ejemplo en el caso del registro R1 , la función f ( x1 ) = x 19 + x 18 + x 17 + x 14 + 1 que representa dicho registro (el cual contiene 19 registros conectados en cascada), toma como salida la operación xor de los bits 19, 18, 17 y 14 (es decir; toma los exponentes de la función para determinar que bits se tomarán en cuenta). Para el registro R2 (de 22 registros conectados en cascada) se toman en cuenta los bits 22 y 21; y finalmente para el registro R3 (23 circuitos conectados en cascada) se consideran los bits 23, 22, 21 y 8. Figura 4a (circuito completo). Figura 4b (un solo registro). El circuito resultante en VHDL de la descripción de los registros (r1, r2, r3) fueron los siguientes: Figura 5. Figura 6. Figura 7. Como se puede apreciar en las figuras 5, 6 y 7, el circuito resultante en esencia fue el mismo, la sola diferencia radica en el tamaño de bits de entrada para cada uno de los circuitos. Las entradas: • • • • data_in <n : 0>: Son los bits de entrada a cargar en cada uno de los registros. clock: Es el reloj del sistema (permite la sincronización del sistema). seleccion<1:0>: Bits que permiten la selección de la señal de entrada. reset: Es el bit permite poner en ceros los contenidos de cada uno de los registros. y las salidas del registro: • regx_out: Representa el bit de salida del registro de desplazamiento. • r_xx: Es el bit central del registro de desplazamiento, el cual permite a la función mayoritaria determinar que registros van a estar en movimiento. Por otro lado, se diseño el componente que controla el movimiento de los tres registros de desplazamiento ( R1 , R2 , R3 ) , es decir la función mayoritaria; permite determinar que registros se desplazaran en base a los bits centrales de cada registro. Es decir, la función recibe “000”; en este caso la mayoría de bits tienen como valor ‘0’ y por lo tanto los registros ( R1 , R2 , R3 ) se desplazaran (un caso similar se suscita cuando la entrada es “111”). En el caso de que la entrada sea “001” la mayoría de bits tienen como valor ‘0’ y por lo tanto los registros R1 y R2 se desplazaran; y el registro R3 quedará intacto. El circuito resultante de implantar esta función se puede observar en la figura 8. Figura 8. Donde las entradas: • • • c <2 : 0>: Son los bits de entrada a la función mayoría (i. e. son los bits centrales de cada uno de los registros). carga: Es el bit de control (en estado alto ‘1’) que permite la carga en paralelo de los datos de entrada (i. e. la llave) dentro de los registros. enable: Bit que permite el desplazamiento (en estado alto ‘1’) de los registros en base al resultado arrojado por la función mayoría. y las salidas del registro: • e<5 : 0>: Representa los bits de habilitación de los registros en base a la siguiente tabla: • • • “00”: sin cambio (mantiene su estado acutal) “01”: carga en paralelo (carga dentro del registro el dato proporcionado por el usuario) “10”: desplazamiento a la derecha (función de corrimiento de bits) Finalmente se implemento el cifrado de flujo de datos empleando el algoritmo A5/1 empleando los circuitos anteriores, se agregan los tres registros junto a la función mayoría, dando como resultado el circuito de la figura 9. Figura 9. Donde las entradas: • key_in<63 : 0>: Es la llave en los registros r1, r2, r3. • carga: Bit que permite la carga de la llave dentro de los registros r1, r2, r3. • clock: Es el reloj del sistema (permite la sincronización del sistema). • data_in: Es el dato a cifrar con la llave. • enable: Es el bit de control que permite realizar el desplazamiento de los registros. • reset: Bit de control que pone en ceros los registros r1, r2, r3. y la salida del registro: • data_out: Representa el bit cifrado. Resultados Los resultados obtenidos de la implementación del algoritmo a5/1 se pueden apreciar en las figuras 10a, 10b. Figura 10a. Figura 10b. En la figura 10a6 y 10b podemos observar que durante la primera transición del reloj, el bit carga esta en alto (‘1’), lo que permite la carga de la llave (que tiene como valor 7014F6019331782h -hexadecimal-), dentro de los registros del algoritmo. En la siguiente transición se observa que se habilita el bit enable (para comenzar a cifrar los datos). La señal en rojo representa la salida (i. e. los datos cifrados). Para este ejemplo se codifico la palabra “Sabel” en ASCII, por lo tomaremos bloques de 7 bits para ver los resultados, la palabra seleccionada en ASCII queda de la siguiente forma: ‘S’ : (1010011)b ‘a’ : (1100001)b ‘b’ : (1100010)b ‘e’ : (1100101)b ‘l’ : (1101100)b 6 La simulación se realizó empleando ModelSim XE II/Starter 5.7c, y la figura resultante es la salida del archivo test_a5.fdo. La salida resultante de esta señal (señal roja), empleando el mismo método de agrupación es: (1011011)b en ASCII corresponde a ‘[‘ (0011110)b en ASCII corresponde a ‘RS‘ (1110000)b en ASCII corresponde a ‘p‘ (1110001)b en ASCII corresponde a ‘q‘ (1010011)b en ASCII corresponde a ‘S‘ De la misma forma procedemos para realizar el proceso inverso (ahora la entrada será la señal obtenida anteroirmente), y se debe de obtener la señal original. Figura 11a. Figura 11b. Primeramente se carga la misma llave que en el ejemplo anterior por lo que se habilita el bit carga, posteriormente se habilita enable (para comenzar a descrifrar el mensaje). La señal en rojo representa la salida (i. e. los datos descifrados), en este caso la entrada es la salida del ejemplo anterior i. e.: ‘[’ : (1011011)b ‘RS’ : (0011110)b ‘p’ : (1110000)b ‘q’ : (1110001)b ‘S’ : (1010011)b La salida resultante de esta señal (señal roja), empleando el mismo método de agrupación es: (1010011)b corresponde a ‘S’ (1100001)b corresponde a ‘a’ (1100010)b corresponde a ‘b’ (1100101)b corresponde a ‘e’ (1101100)b corresponde a‘l’ Por lo que se puede observar gracias a los resultados, se obtiene la señal original del primer ejemplo. Observaciones Emplando la herramienta de Xilinx (Proyect Navigator 6.1.03i), el código sintetizado para la implementación del algoritmo A5/1 dio los siguientes resultados7: ============================================================== =========== * Final Report * ============================================================== =========== Final Results Design Statistics # IOs : 70 Macro Statistics : # Registers : 64 # 1-bit register : 64 # Multiplexers : 64 # 1-bit 4-to-1 multiplexer : 64 # Xors :3 # 1-bit xor4 :3 Cell Usage : # BELS # LUT2 # LUT4 # LUT4_D # LUT4_L # FlipFlops/Latches # FDR # Clock Buffers # BUFGP # IO Buffers # IBUF # OBUF 7 : 139 :3 : 69 :3 : 64 : 64 : 64 :1 :1 : 69 : 68 :1 Los datos fueron tomados a partir del reporte que genera Proyect Navigator, al momento de sintetizar todos los módulos (archivo a5.syr) ============================================================== =========== Device utilization summary: --------------------------Selected Device : v50ecs144-8 Number of Slices: 75 out of 768 9% Number of Slice Flip Flops: 64 out of 1536 4% Number of 4 input LUTs: 139 out of 1536 9% Number of bonded IOBs: 69 out of 98 70% Number of GCLKs: 1 out of 4 25% ============================================================== =========== TIMING REPORT Clock Information: ----------------------------------------------------+------------------------+-------+ Clock Signal | Clock buffer(FF name) | Load | -----------------------------------+------------------------+-------+ clock1 | BUFGP | 64 | -----------------------------------+------------------------+-------+ Timing Summary: --------------Minimum period: 6.044ns (Maximum Frequency: 165.453MHz) Minimum input arrival time before clock: 9.550ns Maximum output required time after clock: 7.237ns Maximum combinational path delay: 6.889ns ============================================================== =========== CPU : 5.97 / 6.85 s | Elapsed : 6.00 / 7.00 s --> Total memory usage is 59292 kilobytes Como se puede observar la frecuencia máxima que puede alcanzar la implementación del algoritmo A5/1 es: 165.453MHz. Y los recursos que más se emplean son los IBOSs, del cual se ocupa 68 IBOSs (es decir el 70% de los IBOSs disponibles). Bibliografía - “Seguridad Informática y Criptografía”, Jorge Ramió Aguirre, Madrid (España) 2003. “Handbook of Applied Cryptography”, de A. Menezes, P. van Oorschot, and S. Vanstone, CRC Press, 1996. “Introduction to Cryptoraphy with Coding Theory”, de Wade Trappe, Lawrence C. Washingtonm, Prentice Hall, New Jersy (U.S.A.), 2002. www.xilinx.com Anexos Códigos fuentes (en VHDL), de cada uno de los circuitos que estas contenidos en el reporte: - ff_d.vhd: Código de un flip-flop tipo D. mux3x1.vhd: Código de un multiplexor de 4x1. r1.vhd: Código del registro R1 . r2.vhd: Código del registro R2 . r3.vhd: Código del registro R3 . a5.vhd: Código del generador LRSF del algoritmo A5/1.