©Mario Medina C. 1

Anuncio

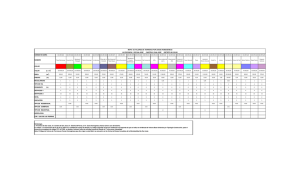

Procesador Y86 Basado en arquitectura Intel x86 z z Procesador Y86 z z Sistemas Computacionales Mario Medina C. [email protected] z z Menos tipos de datos Menos modos de direccionamiento Menos instrucciones Sin punto flotante Sólo opera sobre datos de 32 bits Instrucciones de largo variable Arquitectura del procesador 8 registros visibles al programador z 32 bits Registros generales %eax %ecx %edx %ebx 3 códigos de condición z z z ZF: Zero flag SF: Sign flag OF: Overflow flag Contador de programa (PC) z z Códigos de condición Conjunto de instrucciones %esi %edi %esp %ebp ZF SF OF Contador de programa PC Contiene dirección de instrucción a ejecutar Registro de 32 bits Conjunto de instrucciones Y86 Instrucción Intel x86 movl se divide en 4: z z z z irmovl: inmediato a registro rrmovl: registro a registro mrmovl: memoria a registro rmmovl: registro a memoria 4 operaciones enteras 7 instrucciones de salto Instrucción nop no hace nada Instrucción halt detiene la CPU ©Mario Medina C. addl 6 0 subl 6 1 0 nop 0 0 1 2 3 4 halt 1 0 rrmovl rA, rB 2 0 rA rB irmovl V, rB 3 0 8 rB V rmmovl rA, D(rB) 4 0 rA rB D mrmovl D(rB), rA 5 0 rA rB D OPl rA, rB 6 fn rA rB jXX Dest 7 fn Dest call Dest 8 0 Dest ret 9 0 pushl rA A 0 rA 8 popl rA B 0 rA 8 5 Codificación de instrucciones Instrucciones tienen largo variable z andl 6 2 xorl 6 3 Byte z jmp 7 0 jle 7 1 jl 7 2 je 7 3 jne 7 4 z jge 7 5 z jg 7 6 z Para acomodar argumentos inmediatos y direcciones de memoria Instrucciones de movimiento de datos: 1 byte para especificar registro, 4 bytes para especificar dirección de memoria Instr. aritméticas: 2 bytes, comienzan con 6 Instrucciones de salto: 6 bytes y comienzan con 7 Contador de programa (PC) debe ser modificado en forma acorde 1 Codificación de registros Registro 0: %eax Registro 1: %ecx Registro 2: %edx Registro 3: %ebx Registro 4: %esp Registro 5: %ebp Registro 6: %esi Registro 7: %edi Registro 8: Ninguno Modos de direccionamiento utilizados z z z Indice + desplazamiento (imm(%r)) Dirección efectiva a memoria es imm + %r No hay modos escalados ni indexados con 2 registros Ejemplo de decodificación Qué instrucciones representan las siguientes secuencias de bytes? z z z z z 0x100: 30 83 fc 00 00 10 0x200: a0 68 80 0a 00 00 00 90 0x300: 50 54 07 0x400: 61 13 73 0x500: 63 62 a0 ff ff ff 40 63 00 08 08 02 00 00 10 30 83 00 00 00 00 f0 b0 18 00 04 00 00 10 08 Ejemplo de codificación Codifique las siguientes instrucciones a partir de la posición de memoria 0x100 irmovl $15, %ebx rrmovl %ebx, %ecx Lazo: rmmovl %ecx, -3(%ebx) addl %ebx, %ecx jmp lazo Código ensamblador Intel X86 Suma: pushl %ebp movl %esp, %ebp movl 8(%ebp), %ecx movl 12(%ebp), %edx xorl %eax, %eax testl %edx, %edx je Fin ©Mario Medina C. Lazo: addl (%ecx), %eax addl $4, %ecx decl %edx jnz Lazo Fin: movl %ebp, %esp popl %ebp ret Ejemplo: código C int Sum(int *Start, int Count) { int sum = 0; while (Count) { sum += *Start; Start++; Count--; } return sum; } Código ensamblador Intel Y86 Suma: pushl %ebp rrmovl %esp, %ebp mrmovl 8(%ebp), %ecx mrmovl 12(%ebp), %edx xorl %eax, %eax andl %edx, %edx je Fin .Lazo: mrmovl (%ecx), %esi addl %esi, %ecx irmovl $4, %ebx addl %ebx, %ecx irmovl $-1, %ebx addl %ebx, %edx jne Lazo Fin: rrmovl %ebp, %esp popl %ebp ret 2 Programa completo Intel Y86 .pos 0 // Dir. comienzo codigo Init: irmovl Pila, %esp irmovl Pila, %ebp jmp Main .align 4 Vector: // Define long vector[4] .long 0x000d .long 0x00c0 .long 0x0b00 .long 0xa000 Main: // Programa principal irmovl $4, %eax pushl %eax irmovl Vector, %edx pushl %edx call Suma halt Suma: pushl %ebp rrmovl %esp, %ebp mrmovl 8(%ebp), %ecx mrmovl 12(%ebp), %edx xorl %eax, %eax andl %edx, %edx je Fin .Lazo: mrmovl (%ecx), %esi addl %esi, %ecx irmovl $4, %ebx addl %ebx, %ecx irmovl $-1, %ebx addl %ebx, %edx jne Lazo Fin: popl %ebp ret Pila: .pos 0x100 Salida de ensamblador Yas (1) 0x000: 0x000: 0x006: 0x00c: 0x014: 0x014: 0x018: 0x01c: 0x020: | .pos 0 308400010000 | init: irmovl Pila, %esp 308500010000 | irmovl Pila, %ebp 7024000000 | jmp Main | .align 4 0d000000 | Vector: .long 0xd c0000000 | .long 0xc0 000b0000 | .long 0xb00 00a00000 | .long 0xa000 0x024: 0x02a: 0x02c: 0x032: 0x034: 0x039: 308004000000 a008 308214000000 a028 803a000000 10 Implementación del Y86 Salida de ensamblador Yas (2) 0x03a: 0x03c: 0x03e: 0x044: 0x04a: 0x050: 0x052: 0x057: 0x05d: 0x05f: 0x065: 0x067: 0x06d: 0x06f: 0x074: 0x076: 0x100: a058 2045 501508000000 50250c000000 308000000000 6222 7374000000 506100000000 6060 308304000000 6031 3083ffffffff 6032 7457000000 b058 90 | | | | | | | | | | | | | | | | | | Main: irmovl $4,%eax | pushl %eax # Push 4 | irmovl Vector,%edx | pushl %edx | call Suma | halt Dividiremos el procesamiento de una instrucción en etapas: Suma: pushl %ebp rrmovl %esp,%ebp mrmovl 8(%ebp),%ecx mrmovl 12(%ebp),%edx irmovl $0, %eax andl %edx,%edx je Fin Lazo: mrmovl (%ecx),%esi addl %esi,%eax irmovl $4,%ebx addl %ebx,%ecx irmovl $-1,%ebx addl %ebx,%edx jne Lazo Fin: popl %ebp ret Pila: .pos 0x100 z z z z z z Lectura de instrucción (Fetch) Decodificación de la instrucción (Decode) Ejecución de la operación (Execute) Acceso a memoria (Memory) Actualización de registros (Write Back) Actualización de contador de programa (PC Update) Hardware necesario Unidad Aritmético-Lógica (ALU) z 4 operaciones posibles OP 0: suma OP 1: resta OP 2: AND OP 3: XOR Registros z Program Counter (PC) Memorias z z Para datos Para instrucciones ©Mario Medina C. X Y Banco de registros 8 registros de 32 bits 2 puertos de salida z OP (2 bits) ALU z Leer dos registros al mismo tiempo Seleccionados por señales srcA y srcB 1 puerto de entrada z z Escribir a un registro seleccionado por destW Escribir en el canto de subida del reloj Puerto de salida A Puerto de salida B valA srcA valB srcB (32 bits) (3 bits) (32 bits) (3 bits) Banco de Registros valW dstW (32 bits) (3 bits) Puerto de entrada 3 Flujo de datos procesador Dibujo muestra los flujos de datos de entrada y salida que ocurren en las 6 etapas Hardware (en celeste) consiste en memorias, banco de registros, ALU, PC Ancho de señales proporcionales a número de bits transmitidos Examinaremos etapas en detalles Lee la instrucción a ejecutar de memoria newPC PC Lectura de instrucción (Fetch) valE, valM Write back valM z Data Data memory memory Memory z Addr, Data iCode: identificador de la instrucción a ejecutar iFun: identificador de la función a realizar valE CC CC Execute ALU ALU Bch aluA, aluB z srcA, srcB dstA, dstB icode, ifun rA, rB valC Fetch A B Register Register M file file E valP Instruction Instruction memory memory iCode determina cuántos bytes más se deben leer iCode = 2, 6, 10, 11: 1 byte más iCode = 3, 4, 5: 5 bytes más iCode = 7, 8: 4 bytes más valA, valB Decode Desde posición almacenada en PC Extrae 1er byte, de donde obtiene PC PC increment increment z Calcula la dirección de la próxima instrucción PC iCode y iFun iCode Instrucción 0 nop 1 halt 2 rrmovl 3 irmovl 4 rmmovl 5 mrmovl 6 OP1 7 jXX 8 call 9 ret A pushl B popl iCode define el tipo de instrucción iFun define la función a realizar z z z Si iCode es 6, iFun define la operación Si iCode es 7, iFun define el tipo de salto En otros casos, iFun no es relevante addl 6 0 subl 6 1 andl 6 2 xorl 6 3 jmp 7 0 jle 7 1 jl 7 2 je 7 3 jne 7 4 jge 7 5 jg 7 6 Lee hasta 2 operandos desde el banco de registros Generalmente, campos rA y rB de la instrucción corresponden a srcA y srcB Indican los 2 registros a leer z Instrucciones pushl y popl no necesitan especificar dos registros a usar Usan registro %esp ©Mario Medina C. Salida de registro PC se usa como puntero a memoria de instrucciones z De esta memoria salen iCode, iFun, rA, rB, valC Fetch icode, ifun rA, rB valC Memoria Instruction de Memoria Instruction de instrucciones memory instrucciones memory También es entrada a circuito que incrementa PC z valP Incrementa PC Incrementa PC increment PC increment PC Salida de este circuito es valP PC Decodificación (Decode) z Flujos de datos etapa Fetch Flujo de datos etapa Decode Señales srcA y srcB seleccionan registros a ser leídos Salida es señales valA y valB Señales dstA y dstB seleccionan registros a ser escritos Valores a escribir son valE y valM Decode valA, valB srcA, srcB dstA, dstB A B Banco Banco de de M registros registros E valE, valM 4 Ejecución de operación (Execute) Utiliza la Unidad Aritmético-Lógica (ALU) z z z Para realizar operación aritmético-lógica dada por iFun Para calcular dirección efectiva de referencia a memoria Para incrementar o decrementar el puntero a la pila %esp Resultado de operación se llama valE Operación puede modificar bits de condición z Flujos de datos etapa Execute Señales aluA y aluB son las entradas a la ALU Salida de la ALU se llama valE Bits de condición ZF, SF y OF se almacenan en registro de 3 bits CC Bit Bch indica si debe o no realizarse el salto Acceso a memoria (Memory) aluA, aluB, iFun valE, valM Write Back valM Escritura de datos hacia la memoria Se escriben resultados al banco de registros Memoria Memoria de de datos datos Memory Actualiza PC (PC Update) z ALU ALU newPC PC Update Acceso a registros (Write Back) z CC CC Bch Flujos de datos etapas Memory y Write Back Lectura de datos desde la memoria Valor leído se llama valM z valE Instrucción de salto verifica esos bits Memory,Write Back, PC Update z Execute Addr, Data PC recibe dirección de próxima instrucción a ejecutar Calculada en etapa Fetch Etapas de instrucción OP rA, rB Etapas de rrmovl rA, rB Etapa Instrucción OP rA, rB Etapa rrmovl rA, rB Fetch iCode:iFun ← M1[PC] rA:rB ← M1[PC + 1] valP ← PC + 2 Fetch iCode:iFun ← M1[PC] rA:rB ← M1[PC + 1] valP ← PC + 2 Decode valA ← R[rA] valB ← R[rB] valE ← valB OP valA Set CC Decode Execute Memory Write Back valA ← R[rA] valE ← 0 + valA PC Update PC ← valP Execute Memory Write Back R[rB] ← valE PC Update PC ← valP ©Mario Medina C. R[rB] ← valE 5 Etapas de irmovl V, rB Etapas de rmmovl rA, D(rB) Etapa irmovl V, rB Etapa rmmovl rA, D(rB) Fetch iCode:iFun ← M1[PC] rA:rB ← M1[PC + 1] valC ← M4[PC + 2] valP ← PC + 6 Fetch iCode:iFun ← M1[PC] rA:rB ← M1[PC + 1] valC ← M4[PC + 2] valP ← PC + 6 valA ← R[rA] valB ← R[rB] valE ← valB + valC M4[valE] ← valA Decode Execute Memory Write Back PC Update Decode valE ← 0 + valC R[rB] ← valE Execute Memory PC ← valP Write Back PC Update Etapas de mrmovl D(rB), rA PC ← valP Etapas de pushl rA Etapa mrmovl D(rB), rA Etapa pushl rA Fetch Fetch iCode:iFun ← M1[PC] rA:rB ← M1[PC + 1] valP ← PC + 2 Decode Decode Execute Memory Write Back iCode:iFun ← M1[PC] rA:rB ← M1[PC + 1] valC ← M4[PC + 2] valP ← PC + 6 valB ← R[rB] valE ← valB + valC valM ← M4[valE] R[rA] ← valM Execute Memory Write Back valA ← R[rA] valB ← R[%esp] valE ← valB + (-4) M4[valE] ← valA R[%esp] ← valE PC Update PC ← valP PC Update PC ← valP Etapas de popl rA Etapas de jXX Dest Etapa popl rA Etapa jXX Dest Fetch iCode:iFun ← M1[PC] rA:rB ← M1[PC + 1] valP ← PC + 2 Fetch iCode:iFun ← M1[PC] valC ← M4[PC + 1] valP ← PC + 5 Decode valA ← R[%esp] valB ← R[%esp] valE ← valB + 4 valM ← M4[valA] R[%esp] ← valE R[rA] ← valM PC ← valP Decode Execute Memory Write Back Execute Memory Write Back PC Update ©Mario Medina C. PC Update Bch ← Cond(CC, iFun) PC ← Bch ? valC : valP 6 Etapas de call Dest Etapas de ret Etapa call Dest Etapa ret Fetch iCode:iFun ← M1[PC] valC ← M4[PC + 1] valP ← PC + 5 Fetch iCode:iFun ← M1[PC] valP ← PC + 1 Decode Execute Memory Write Back valB ← R[%esp] valE ← valB + (-4) M4[valE] ← valP R[%esp] ← valE Decode valA ← R[%esp] valB ← R[%esp] PC Update PC ← valC Execute Memory Write Back valE ← valB + 4 valM ← M4[valA] R[%esp] ← valE PC Update PC ← valM Código ejemplo 1. 2. 3. 4. 5. 6. 7. 8. 9. 10. 11. 0x000: 0x006: 0x00c: 0x00e: 0x014: 0x01a: 0x01c: 0x01e: 0x023: 0x028: 0x029: 300209000000 308315000000 6123 308480000000 404364000000 a028 b008 7328000000 8029000000 10 90 | irmovl $9, %edx | irmovl $21, %ebx | subl %edx, %ebx | irmovl $128, %esp | rmmovl %esp, 100(%ebx) | pushl %edx | popl %eax | je done | call proc | done: halt | proc: ret Análisis de la 3ra instrucción Etapa Instrucción OP rA, rB Fetch iCode:iFun ← M1[PC] iCode:iFun rA:rB ← M1[PC + 1] ←M1[0x00c]=6:1 rA:rB ← M1[0x00d]=2:3 valP ← PC + 2 valP ←0x00c+2=0x00e valA ← R[rA] valA ← R[%edx]=9 valB ← R[rB] valB ← R[%ebx]=21 valE ← valB OP valA valE ← 21 - 9 = 12 Set CC ZF ←0, SF ←0, OF ←0 Decode Execute Memory Write Back R[rB] ← valE R[%ebx] ← 12 PC Update PC ← valP PC ← valP=0x00e Análisis de la 4ta. instrucción Etapa Fetch Análisis de la 5ta. Instrucción irmovl $128, %esp Etapa rmmovl rA, rB rmmovl %esp, 100(%ebx) iCode:iFun←M1[PC] rA:rB←M1[PC + 1] valC ← M4[PC + 2] valP ← PC + 6 iCode:iFun←M1[0x00e]=3:0 rA:rB ← M1[0x00f]=8:4 valC ← M4[0x010]=0x80 valP ← 0x00e + 6=0x014 Fetch iCode:iFun←M1[PC] rA:rB←M1[PC + 1] valC←M4[PC + 2] valP ← PC + 6 iCode:iFun ← rA:rB ← valC ← valP ← Decode valE ← 0 + valC valE ← 0 + 0x80 valA ← R[rA] valB ← R[rB] valE ← valB + valC M4[valE] ← valA valA ← valB ← valE ← M 4[ ] ← irmovl rA, rB Decode Execute Subl %edx, %ebx Write Back R[rB] ← valE R[%esp] ← 0x80 Execute Memory Write Back PC Update PC ← valP PC ← 0x014 PC Update PC ← valP Memory ©Mario Medina C. PC ← 7 Análisis de la 6ta. Instrucción Análisis de la 7ta. Instrucción Etapa pushl rA pushl %edx Etapa popl rA popl %eax Fetch iCode:iFun ← M1[PC] rA:rB ← M1[PC + 1] valP ← PC + 2 Fetch Decode valA ← R[rA] valB ← R[%esp] iCode:iFun←M1[0x01a] iCode:iFun ←a:0 rA:rB ← M1[0x01b]=2:8 valP ← 0x01a+2=0x01c valA ← R[%edx] = 9 valB ← R[%esp] = 128 iCode:iFun ← M1[PC] rA:rB ← M1[PC + 1] valP ← PC + 2 valA ← R[%esp] valB ← R[%esp] valE ← valB + 4 iCode:iFun ← M1[ rA:rB ← M1[ ] valP ← valA ← valB ← valE ← Execute valE ← valB + (-4) valE ← 128+(-4)=124 Memory valM ← M4[valA] valM ← Memory M4[valE] ← valA M4[124] ← 9 Write Back R[%esp] ← valE R[rA] ← valM R[%esp] ← R[rA] ← PC Update PC ← valP PC ← Write Back R[%esp] ← valE R[%esp] ← 124 PC Update PC ← valP PC ← 0x01c Decode Execute Análisis de la 8va. Instrucción ] Análisis de la 9na. Instrucción Etapa jXX Dest je 0x028 Etapa call Dest Call 0x029 Fetch iCode:iFun←M1[PC] valC←M4[PC + 1] valP←PC + 5 iCode:iFun ← M1[0x01e] iCode:iFun ← 7:3 valC ← M4[0x01f]=0x028 valP ← 0x01e+5=0x023 Fetch iCode:iFun ← M1[PC] valC ← M4[PC + 1] valP ← PC + 5 iCode:iFun ← M1[ ] valC ← M4[ ] valP ← Decode valB ← R[%esp] valB ← Execute valE ← valB + (-4) valE ← Memory M4[valE] ← valP M 4[ ] ← Write Back R[%esp] ← valE R[ ] ← PC Update PC ← valC PC ← Decode Execute Bch←Cond(CC, iFun) Bch ← Cond((0, 0, 0), 3) Memory Write Back PC Update PC ← Bch?valC : valP PC← 0 ? 0x028 : 0x023 PC ← 0x023 Análisis de la 11ma. Instrucción Etapa ret ret Fetch iCode:iFun←M1[PC] valP ← PC + 1 iCode:iFun ← M1[0x029] iCode:iFun ← 9:0 valP ← 0x029+1=0x02a Decode valA ← R[%esp] valB ← R[%esp] valA ← R[%esp]=124 valB ← R[%esp]=124 Execute valE ← valB + 4 valE ← 124+4=128 Memory valM ← M4[valA] valM ← M4[124]=0x028 Write Back R[%esp] ← valE R[%esp] ← 128 PC Update PC ← valM PC ← 0x028 ©Mario Medina C. Implementación secuencial SEQ Toda instrucción de Y86 puede descomponerse en 6 etapas: z Fetch, Decode, Execute, Memory, Write Back, PC Update Cada etapa tiene su rol específico que cumplir en cada instrucción z Detallada en las tablas anteriores Cómo implementar este procesador? z z Implementación secuencial SEQ Ejecuta una instrucción en 1 ciclo de reloj 8 Diagrama Implementación SEQ HW de Implementación SEQ Hardware: rectángulos celestes z Memoria, ALU, registros, etc. Memoria y registros activados por reloj Bloques de control: rectángulos grises z Circuitos combinacionales Señales: nombres en círculos blancos z Grosor representa número de bits Etapas Fetch y Decode valA valB Etapa Execute dstE dstM srcA srcB Bch valE CC CC ALU ALU dstE dstM srcA srcB Execute Decode A ALU fun. B Register Register M file file ALU A E ALU B Write back icode ifun rA rB valC valP valC Fetch Instruction Instruction memory memory valA valB PC PC increment increment PC Etapas Memory , PC Update newPC New PC valM data out read Mem. control write Data Data memory memory Addr Data Implementación Etapa Fetch Se leen hasta 6 bytes desde la memoria, partiendo desde PC Bloque especial incrementa PC y genera valP De la instrucción, salen iCode, iFun, rA, rB y valC icode ifun rA rB valC valP Need valC Instr valid Need regids Split Split PC PC increment increment Align Align Byte 0 Bytes 1-5 Instruction Instruction memory memory PC Bch valA valE ©Mario Medina C. valP 9 Implementación etapa Decode Instrucción determina 2 registros para lectura y/o 2 registros para escritura z z Implementación etapa Execute ALU z valA valB valM valE z A B Banco Banco de de Registros Registros Valores leídos son valA y valB Valores a escribir son valM y/o valE dstE dstM Códigos de condición CC (ZF, SF, OF) son calculados en base al resultado de la operación realizada M E srcA srcB dstE dstM srcA srcB En etapa Write Back icode rA Realiza operación OP Calcula dirección efectiva z rB z Mem. write iCode determina si se realiza una lectura o una escritura z read Data Data memory memory z z write Mem addr valE icode Mem data 1 0x000: irmovl $0x100,%ebx Ciclo 4 2 3 4 z # %ebx <-- 0x100 Ciclo 2: 0x006: irmovl $0x200,%edx # %edx <-- 0x200 Ciclo 3: 0x00c: addl %edx,%ebx # %ebx <-- 0x300 CC <-- 000 Ciclo 4: 0x00e: je dest # Not taken Ciclo 5: 0x013: rmmovl %ebx,0(%edx) # M[0x200] <-- 0x300 ©Mario Medina C. valB PC icode Bch valC valM valP Ejemplo de sincronización (1) Clock Ciclo 1: valA valA valP z Ciclo 3 ALU B New PC Comienzo de ejecución ciclo 3 Ciclo 2 ALU A valC valC valM valP dependiendo de los valores de iCode y Bch Sincronización de SEQ Ciclo 1 Set CC icode ifun ALU fun. ALU ALU CC CC Implementación PC Update data out Valor de salida se llama valM bcond bcond El nuevo valor de PC puede ser: valM Mem. read valE Bit Bch indica si comparación bcond es verdadera o falsa Implementación etapa Memory La memoria de datos escribe valA ó valP en la dirección dada por valE o valA Bch z Ejecución de instrucción addl %edx, %ebx Estado definido por instrucción anterior irmovl $0x200, %edx Estado de bits de condición Comienzo del ciclo 3 Lógica Combinacional CC CC 100 100 Lectura Escritura Memoria Memoria de de datos datos Puertos de lectura Puertos escritura Banco Banco de de registros registros %ebx %ebx = = 0x100 0x100 ZF = 1, SF = 0, OF = 0 PC 0x00c 10 Ejemplo de sincronización (2) Final de ejecución ciclo 3 z z z z Estado final de instrucción addl %edx, %ebx Nuevo valor de %ebx es 300 Nuevo valor de PC es 0x00e Nuevo valor de bits de condición Comienzo de ejecución ciclo 4 Final de ciclo 3 z Lógica Combinacional CC CC 100 100 Lectura Cúando se transpasan los valores calculados? En el canto de subida del reloj Escritura Memoria Memoria de de datos datos Puertos Lectura 000 z Puertos Escritura Banco Banco de de registros registros ZF = 0, SF = 0, OF = 0 z Ejemplo de sincronización (3) %ebx <-0x300 %ebx %ebx = = 0x100 0x100 PC 0x00c Estado inicial de instrucción je dest Estado generado por instrucción anterior está reflejado en el PC, memoria, banco de registros y códigos de condición. Comienzo de ciclo 4 Lógica Combinacional CC CC 000 000 Pero no aún en el circuito combinacional Lectura Escritura Memoria Memoria de de datos datos Puertos Lectura Puertos Escritura Banco Banco de de registros registros %ebx %ebx = = 0x300 0x300 0x00e PC 0x00e Ejemplo de sincronización (4) Final de ejecución ciclo 4 z z Estado final de instrucción je dest Condición del salto determinado por PC, memoria, banco de registros y códigos de condición actuales Final de ciclo 4 Lógica Combinacional CC CC 000 000 Memoria Memoria de de datos datos Puertos Lectura ZF = 0 indica salto no se realiza Nuevo valor para PC: 0x013 %ebx %ebx = = 0x300 0x300 PC 0x00e ©Mario Medina C. Puertos escritura Banco Banco de de registros registros 0x013 11