TP1_TC2016.pdf

Anuncio

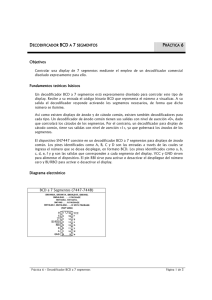

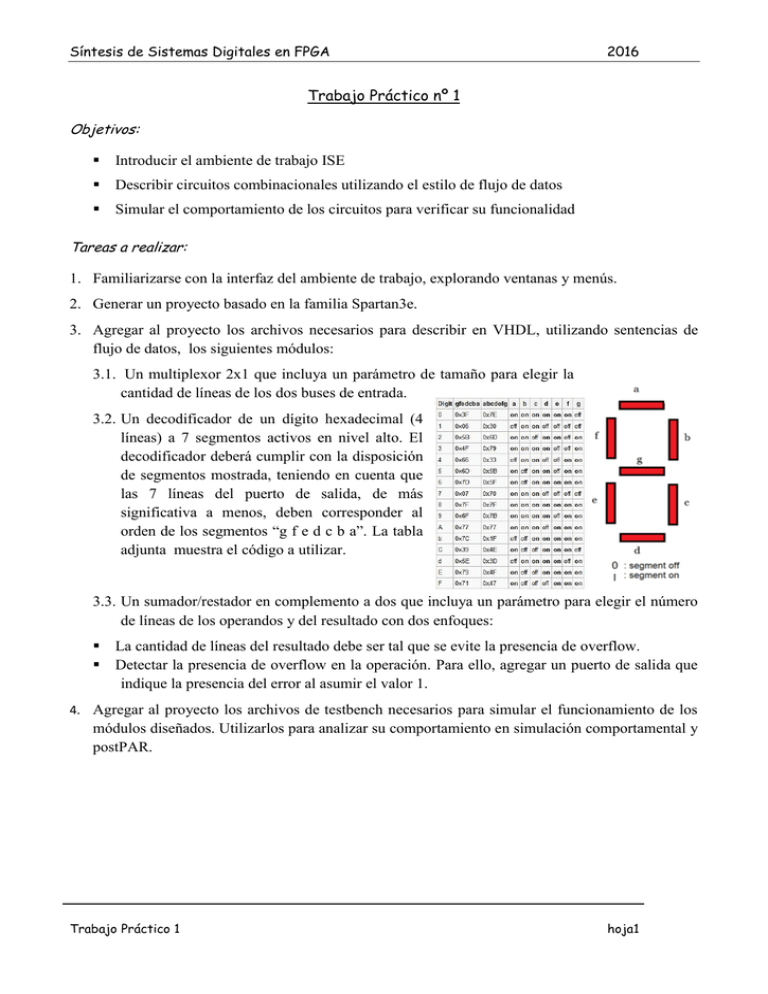

Síntesis de Sistemas Digitales en FPGA 2016 Trabajo Práctico nº 1 Objetivos: Introducir el ambiente de trabajo ISE Describir circuitos combinacionales utilizando el estilo de flujo de datos Simular el comportamiento de los circuitos para verificar su funcionalidad Tareas a realizar: 1. Familiarizarse con la interfaz del ambiente de trabajo, explorando ventanas y menús. 2. Generar un proyecto basado en la familia Spartan3e. 3. Agregar al proyecto los archivos necesarios para describir en VHDL, utilizando sentencias de flujo de datos, los siguientes módulos: 3.1. Un multiplexor 2x1 que incluya un parámetro de tamaño para elegir la cantidad de líneas de los dos buses de entrada. 3.2. Un decodificador de un dígito hexadecimal (4 líneas) a 7 segmentos activos en nivel alto. El decodificador deberá cumplir con la disposición de segmentos mostrada, teniendo en cuenta que las 7 líneas del puerto de salida, de más significativa a menos, deben corresponder al orden de los segmentos “g f e d c b a”. La tabla adjunta muestra el código a utilizar. 3.3. Un sumador/restador en complemento a dos que incluya un parámetro para elegir el número de líneas de los operandos y del resultado con dos enfoques: La cantidad de líneas del resultado debe ser tal que se evite la presencia de overflow. Detectar la presencia de overflow en la operación. Para ello, agregar un puerto de salida que indique la presencia del error al asumir el valor 1. 4. Agregar al proyecto los archivos de testbench necesarios para simular el funcionamiento de los módulos diseñados. Utilizarlos para analizar su comportamiento en simulación comportamental y postPAR. Trabajo Práctico 1 hoja1