TP4_TC2016.pdf

Anuncio

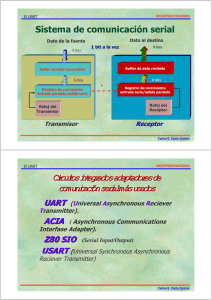

Síntesis de sistemas digitales en FPGA 2016 Trabajo Práctico nº 4 Objetivos: Describir un sistema jerárquico utilizando estilo estructural. Aplicar conceptos de codiseño Hardware / Software. Incorporar al diseño IP cores de libre distribución. Simular el comportamiento del sistema para verificar su funcionalidad Implementar el circuito en la placa de desarrollo Tareas a realizar: 1. Diseñar un sistema con un PB embebido para ser implementado en la placa de desarrollo. En las cuatro primeras direcciones de la memoria interna del PB se almacenarán los datos hexadecimales 00, 05, 10, 28. Desde una PC se envían caracteres al PB (utilizando el puerto RS 232 de la placa Digilent). Si el caracter recibido no es un número, se encenderán todos los leds. Si el caracter recibido es un número: Si es impar, se presentará en los leds su C2 Si es par, se realizará el promedio entero entre el dato leído y el dato guardado en la primera dirección de la memoria interna del PB, presentándose el resultado en los leds. El siguiente dato par se deberá promediar con el contenido de la dirección siguiente, y así sucesivamente, hasta utilizar el cuarto dato almacenado. Cuando esto ocurra, el siguiente dato par que ingrese se promediará con el primer dato almacenado y se repetirá el comportamiento. 2. Ensamblar y simular para analizar el comportamiento definido en el archivo EjemploPico.psm, utilizando el ambiente IDE. Verificar que la herramienta construye el archivo aplicación.vhd, que describe el módulo de memoria que contiene el programa. 3. En el ambiente ISE, integrar en un módulo estructural, el core de PicoBlaze y la memoria del programa. Para ello agregar en un proyecto los archivos KCPSM3.vhd, Top.vhd, y aplicación.vhd. Verificar mediante el Esquemático RTL que genera el ambiente, la interconexión de los módulos. 4. Completar el diseño en ISE, integrando en un estructural general el módulo TOP logrado en el punto anterior, la UART (con su generador de frecuencia de referencia), y dos módulos (Reg) idénticos para registrar adecuadamente la salida de la UART y del Pico. Para ello se sugiere completar el diseño de la siguiente forma: Trabajo Práctico 4 hoja1 Síntesis de sistemas digitales en FPGA Divisor Reg1 2016 Pico Reg2 UART Los módulos Reg1 y Reg2, son registros con habilitación y reset. Prestar atención con Reg1, cuya habilitación está dada por la señal interrupt_ack. 5. Simular en ISE el funcionamiento del sistema completo para verificar su correcto funcionamiento. 6. Definir el archivo ucf con la asignación de pines correspondientes a las entradas y salidas del sistema completo. 7. Implementar el diseño y obtener el archivo .bit correspondiente para programar la FPGA de la placa Digilent, con el objetivo de verificar el comportamiento final del sistema. Trabajo Práctico 4 hoja2