Plancha_VHDL_2010.pdf

Anuncio

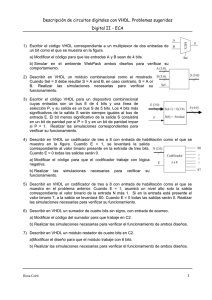

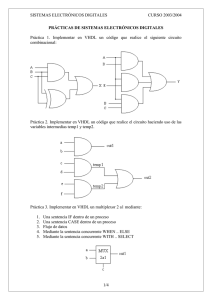

Descripción de circuitos digitales con VHDL. Problemas sugeridos Digital II - ECA 1) Escribir el código VHDL correspondiente a un multiplexor de dos entradas de un bit como el que se muestra en la figura. a) Modificar el código para que las entradas A y B sean de 4 bits. b) Simular en el ambiente WebPack ambos diseños para verificar su comportamiento. 2) Describir en VHDL un módulo combinacional como el mostrado. Cuando Sel = 0 debe resultar S = A and B, en caso contrario, S = A or B. a) Agregar una entrada de habilitación E, de forma que cuando E = 0, S = “1111”, caso contrario se comporta como estaba previsto. b) Realizar las simulaciones necesarias para verificar su funcionamiento. 3) Escribir el código VHDL para un dispositivo combinacional cuyas entradas son un bus E de 4 bits y una línea de selección P, y su salida es un bus S de 5 bits. Los 4 bits más significativos de la salida S serán siempre iguales al bus de entrada E. El bit menos significativo de la salida S consistirá en un bit de paridad par si P = 0 y en un bit de paridad impar si P = 1. Realizar las simulaciones correspondientes para verificar su funcionamiento. 4) Describir en VHDL un codificador de tres a 8 con entrada de habilitación como el que se muestra en la figura. Cuando E = 1, se levantará la salida correspondiente al valor binario presente en la entrada de tres bits. Cuando E = 0 todas las salidas serán 0. a) Modificar el código para que el codificador trabaje con lógica negativa. b) Realizar las simulaciones necesarias para verificar su funcionamiento. 5) Describir en VHDL un codificador de tres a 8 con entrada de habilitación como el que se muestra en el problema anterior. Cuando E = 1, asumirá un nivel alto solo la salida correspondiente al valor binario de la entrada N más 1. Si en la entrada está presente el valor binario 7, a la salida se levantará S0. Cuando E = 0 todas las salidas serán 0. Realizar las simulaciones necesarias para verificar su funcionamiento. 6) Describir en VHDL un sumador de cuatro bits sin signo, con entrada de acarreo. a) Modificar el código del sumador para que trabaje en C2. b) Realizar las simulaciones necesarias para verificar el funcionamiento de ambos diseños. 7) Describir en VHDL un módulo restador de cuatro bits en C2. a)Modificar el diseño para que el módulo trabaje con 6 bits. b) Realizar las simulaciones necesarias para verificar el funcionamiento de ambos diseños. Rosa Corti 1 Descripción de circuitos digitales con VHDL. Problemas sugeridos Digital II - ECA 8) Escribir el código VHDL correspondiente a un FFD con reset asincrónico y señal de habilitación de reloj. Simular en el ambiente de diseño para verificar su funcionamiento. 9) Escribir el código VHDL correspondiente a un FFJK con reset asincrónico. Simular en el ambiente de diseño para verificar su funcionamiento. 10) Escribir el código VHDL de un módulo como el mostrado, capaz de presentar en todo momento en la salida S el promedio de las palabras A y B de ocho bits, interpretadas como números sin signo. a) Modificar el diseño de forma que las palabras A y B se interpreten como enteros en C2. b) Incorporar al módulo dos entradas, una de reloj y la otra correspondiente a un reset asincrónico prioritario, que lleva a la salida S a cero cuando asume el valor alto. Cuando el reset es 0, el módulo deberá actualizar el valor de S en sincronismo con la señal de reloj. c) Simular los tres diseños en el ambiente de trabajo para verificar un correcto funcionamiento. 11) Describir en VHDL un registro de desplazamiento de 4 bits, con reset R asincrónico prioritario y entrada de habilitación E como se muestra en la figura. Si el reset es 0, y la habilitación es 0, el registro conserva su valor anterior. Si el reset es 0 y se habilita el funcionamiento, el registro ingresará desplazando hacia la izquierda, el valor que se encuentra en la entrada serie I. En la salida S de un bit, se presenta el bit más significativo del valor que almacena el registro a) Modificar el código para que el registro funcione en forma análoga, pero desplazando a la derecha. b) Simular en el ambiente WebPack para verificar el correcto funcionamiento de los diseños. 12) Describir en VHDL un fasímetro de 8 fases como el mostrado. El mismo cuenta con un reset sincrónico y, en todo momento, sólo una de sus salidas es 1, permaneciendo las otras en nivel bajo. El comportamiento del bloque deberá ser el siguiente: Cuando RF está en nivel alto, con cada flanco activo del reloj F0 asumirá el valor 1 y las restantes fases permanecerán en nivel bajo. Al caer RF a 0, el dispositivo quedará habilitado para mover el nivel alto a la fase siguiente con cada flanco de reloj, siguiendo la secuencia F0, F1, F2,…, F6, F7, F0, F1 y así sucesivamente. Simular el funcionamiento del bloque para verificar su comportamiento. 13) Escribir el código VHDL para un contador de 8 bits, con reset sincrónico y habilitación de cuenta, capaz de cargar un valor inicial en paralelo y de contar en forma ascendente/descendente. La prioridad de las señales de control debe ser: Reset, Load, Enable. Se deberá incluir una señal que defina el sentido de la cuenta. a) Modificar el diseño para que el reset sea sincrónico b) Modificar el diseño para que al contar incremente/decremente de a dos unidades. Rosa Corti 2 Descripción de circuitos digitales con VHDL. Problemas sugeridos Digital II - ECA c) En todos los casos simular el diseño para verificar su funcionamiento. 14) Diseñar un dispositivo VHDL como el mostrado. El mismo cuenta con un reset sincrónico prioritario que debe garantizar que S sea 0 y que el dispositivo quede en condiciones de iniciar su funcionamiento. Mientras el reset está en nivel bajo, el dispositivo trabaja con las siguientes pautas: La salida S asume un nivel alto cuando las entradas A y B han sido simultáneamente 1 en siete bit-times, y permenece en dicho estado durante dos bit-times, siendo 0 en todo otro momento. Una vez transcurridos los 2 bit-times en los que permanece en 1, S vuelve a cero y se repite el comportamiento del dispositivo en forma indefinida. Simular el diseño en el ambiente de trabajo para verificar su funcionamiento. 15) Diseñar un dispositivo VHDL como el mostrado, que debe interpretar los valores de las entradas A y B como números en C2. Las salidas deben comportarse de la siguiente manera: Salida M: cuando Reset = 1, M = 0. Si Reset = 0 entonces M estará siempre constituida por los dos bits más significativos de A seguidos por los dos bits más significativos de B. En este último caso debe actualizar su valor cada vez que A o B cambien, sin importar otras entradas. Salida S: Reset = 1 prioritario la enviará en forma sincrónica con Clk a cero. Si Reset = 0 S permanece todavía en cero hasta que A y B asumen el valor 1111 en forma simultánea durante un bit-time. A partir de ese momento en forma sincrónica con Clk, asumirá siempre el valor correspondiente al mayor entre A y B. Si Reset = 1 nuevamente, deberá repetir el mismo comportamiento. 16) Diseñar un dispositivo VHDL como el mostrado, que debe interpretar los valores de las entradas A y B como números en C2. El dispositivo cuenta con un reset asincrónico prioritario que cuando asume un valor alto debe garantizar que las salidas S y M sean 0. Si el reset está en un valor bajo, el módulo actualizará el valor de S sincrónicamente con clk de la siguiente forma: Cuando sel = “01”, S = A + B Cuando sel = “10”, S será igual a su valor anterior con un bit rotado a la izquierda. En todo otro caso, S conservará el valor que tenía. La salida M del módulo también se actualizará con la señal de reloj, asumiendo el valor 1 si A > B y cero en caso contrario. Se deberá establecer el número n de bits de S, para que el resultado presentado sea siempre correcto. Simular en el ambiente WebPack el funcionamiento del dispositivo para verificar que responde a lo solicitado. Rosa Corti 3